Question

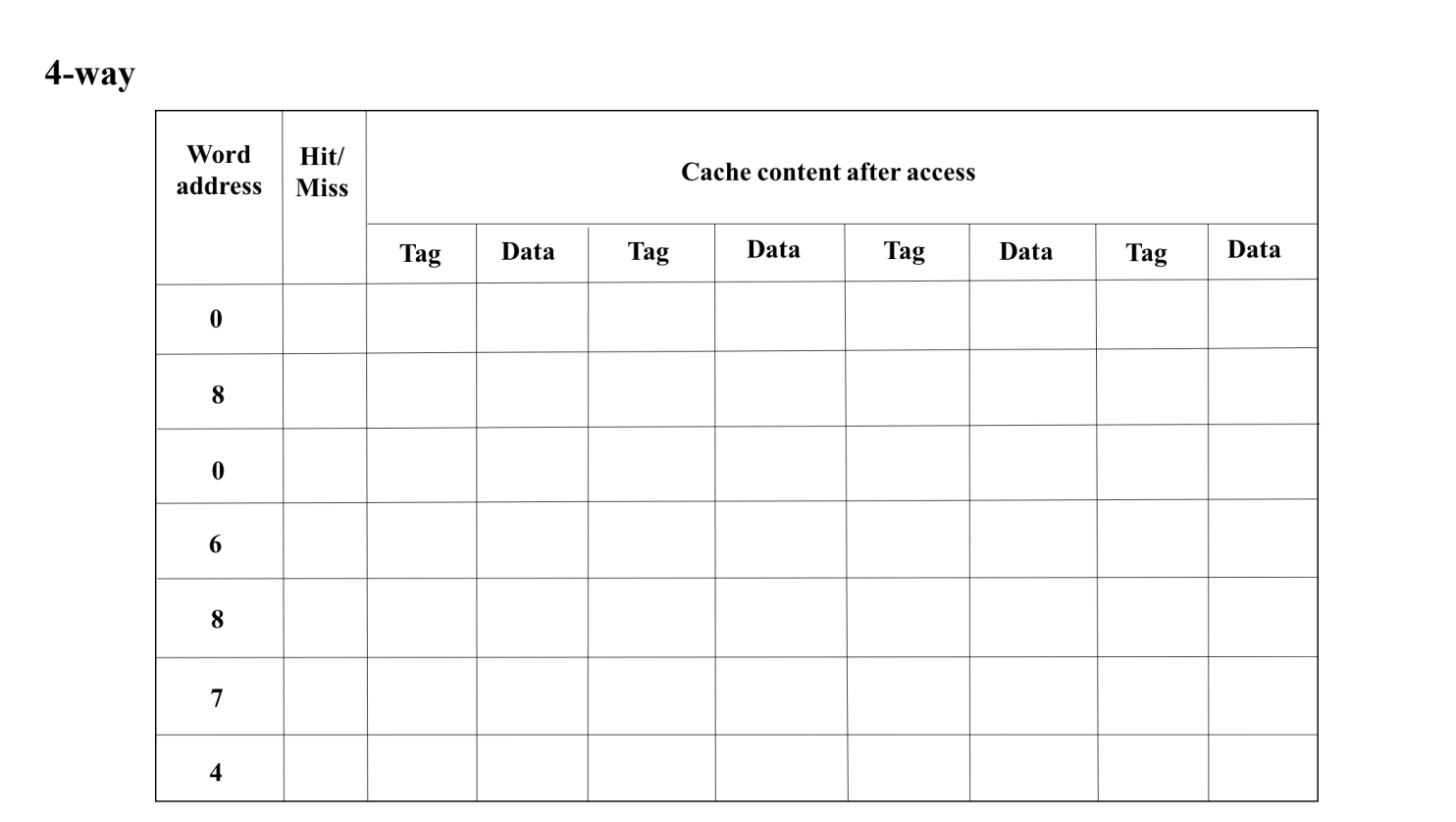

Consider a word address sequence: 0, 8, 0, 6, 8, 7, 4 for a 4-block cache designed in 3 different ways, viz., Direct mapped, 2-way

Consider a word address sequence: 0, 8, 0, 6, 8, 7, 4 for a 4-block cache designed in 3 different ways, viz., Direct mapped, 2-way set-associative, and 4-way set associative. Considering 1-word/block cache design and LRU replacement strategy, enter relevant values in the boxes below. Use binary values, except for the data part in cache (for the data part, use Mem[0] to denote memory content of address 0). Ignore the word/byte offsets, and the valid bit when calculating the number of bits in the Tag field. Helpful Note: With associativity, the number of bits in the tag field generally increases irrespective of whether those extra bits are required or not.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started