Question

Consider the following codes. I) Loop: L.D II) Loop: f0, 0(rl) ADD.D f4, f0, f2 S.D f4, 0(rl) ADDI rl, r1, #23-8 BNE rl,

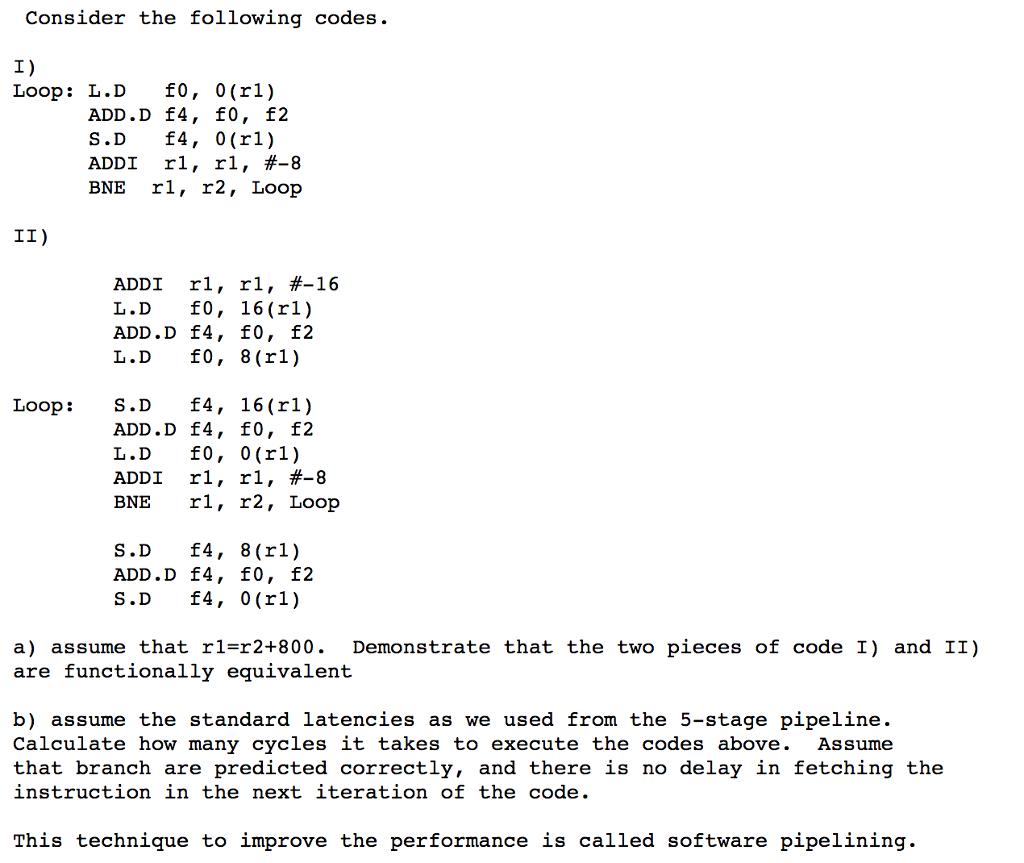

Consider the following codes. I) Loop: L.D II) Loop: f0, 0(rl) ADD.D f4, f0, f2 S.D f4, 0(rl) ADDI rl, r1, #23-8 BNE rl, r2, Loop ADDI rl, r1, #2-16 L.D f0, 16(rl) ADD.D f4, f0, f2 L.D f0, 8(rl) S.D f4, 16(rl) ADD.D f4, f0, f2 L.D f0, 0(rl) ADDI rl, r1, #23-8 BNE r1, r2, Loop S.D f4, 8(rl) ADD.D f4, f0, f2 S.D f4, 0(rl) a) assume that rl=r2+800. Demonstrate that the two pieces of code I) and II) are functionally equivalent b) assume the standard latencies as we used from the 5-stage pipeline. Calculate how many cycles it takes to execute the codes above. Assume that branch are predicted correctly, and there is no delay in fetching the instruction in the next iteration of the code. This technique to improve the performance is called software pipelining.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Computer Architecture A Quantitative Approach

Authors: John L. Hennessy, David A. Patterson

4th edition

123704901, 978-0123704900

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App