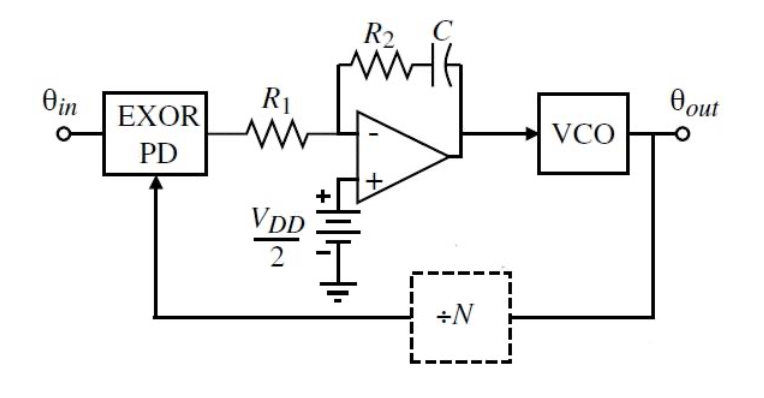

Question: Consider the PLL shown in Figure Q2. Assume that: i) the phase detector is a simple CMOS EXOR whose logic levels are ground and VDD

Consider the PLL shown in Figure Q2. Assume that: i) the phase detector is a simple CMOS EXOR whose logic levels are ground and VDD = 5V, ii) both the input to the loop and the VCO output are square waves that swing between ground and VDD, and iii) the VCO has a perfectly linear relationship between the control voltage and output frequency of 10 MHz/V. The polarities are such that an increase in control voltage causes an increase in the VCO frequency.

Figure Q2

(a) Derive the expression for the closed-loop transfer function ?out(s)/?in(s) and the loop gain.

(b) Assume R2 = 0 and R1 = 10 k?. What value of C gives a loop crossover frequency of 100 kHz? What is the phase margin? Assume the op-amp is ideal.

Oin EXOR PD R www VDD 2 |H R C 46 +N VCO out

Step by Step Solution

3.34 Rating (148 Votes )

There are 3 Steps involved in it

To solve this problem well analyze the phaselocked loop PLL system a Derive the expression for the closedloop transfer function ThetatextoutsThetatext... View full answer

Get step-by-step solutions from verified subject matter experts