Question: Course: Computer Architecture and Organisation Can you solve this Exercise 5? The exercise mentions 3 slides. (The ones given in slides 14, 15, 16 and

Course: Computer Architecture and Organisation

Can you solve this Exercise 5? The exercise mentions 3 slides.

(The ones given in slides 14, 15, 16 and 17) are below:

(The ones given in slides 14, 15, 16 and 17) are below:

![and 17) are below: Exercise 5 [1.5pts] If we have three different](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f467a290b26_34566f467a1ea06c.jpg)

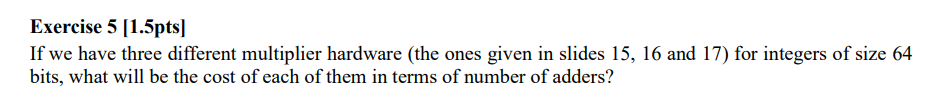

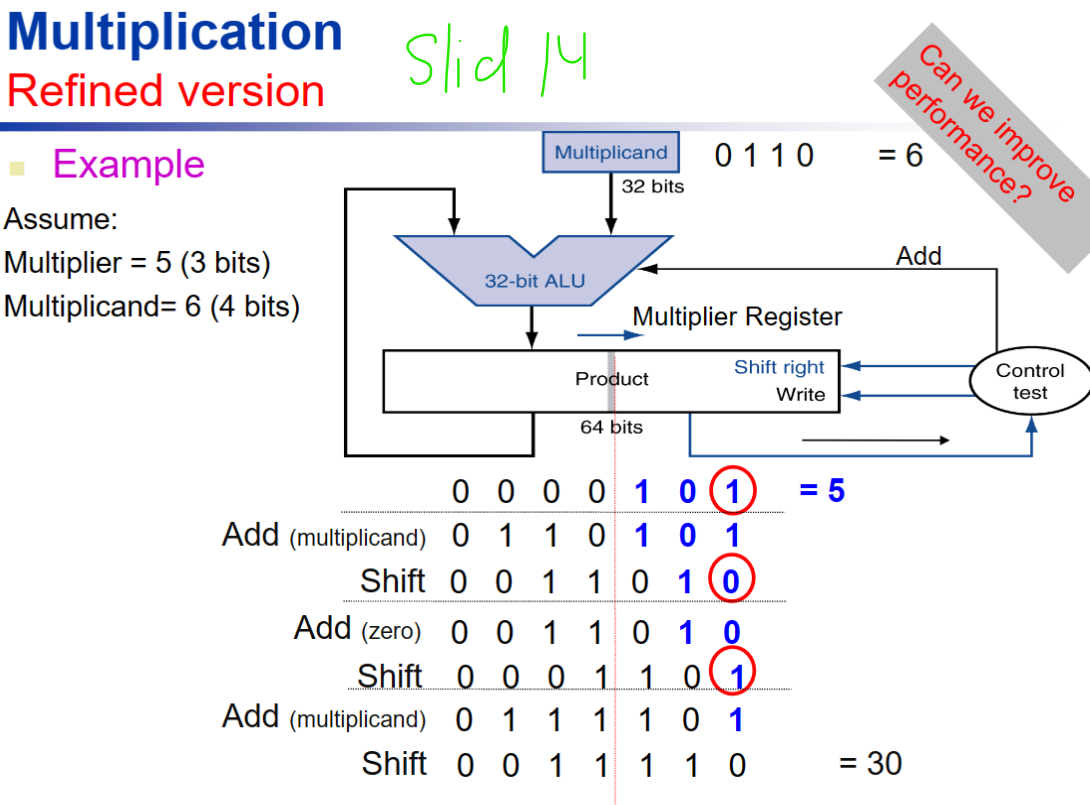

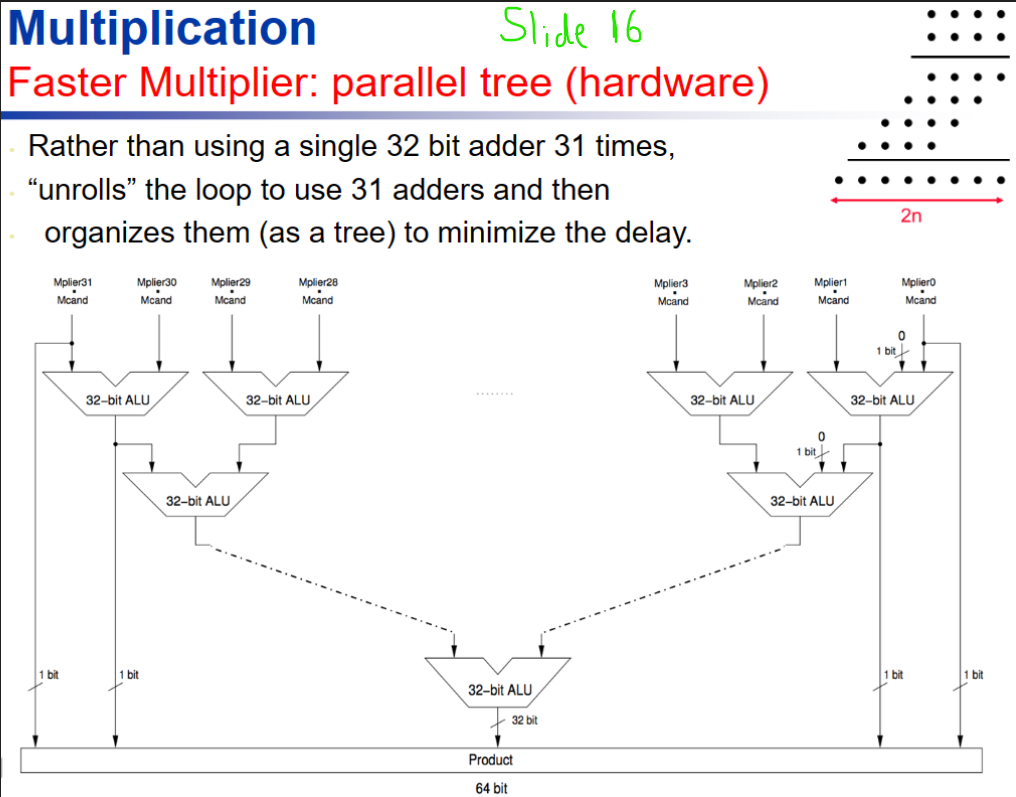

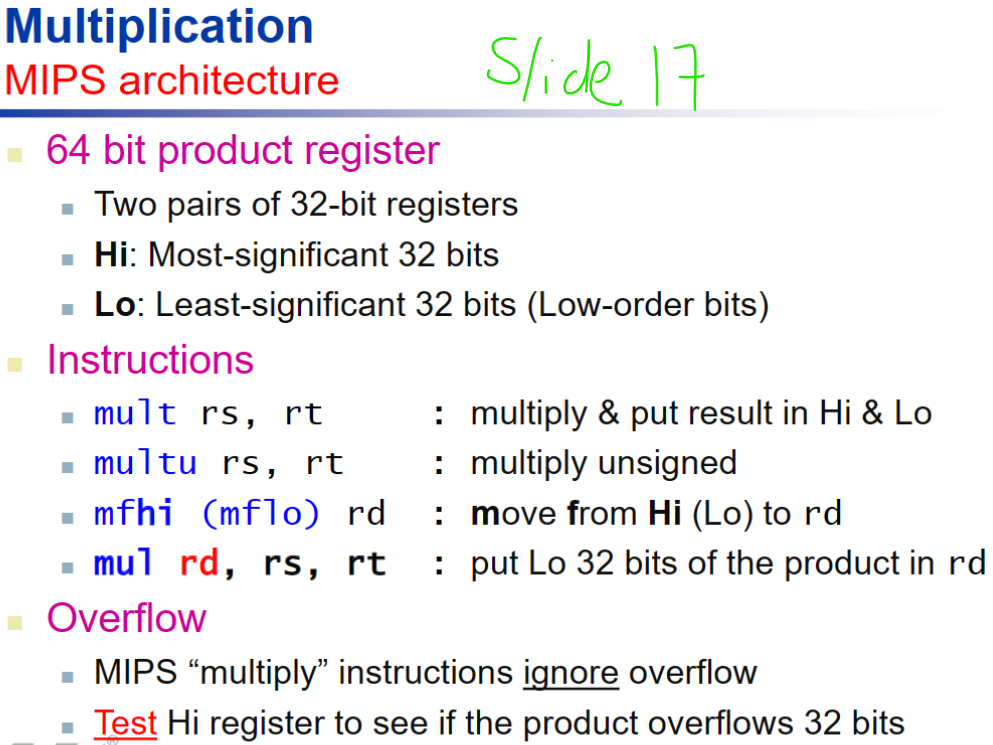

Exercise 5 [1.5pts] If we have three different multiplier hardware (the ones given in slides 15,16 and 17) for integers of size 64 bits, what will be the cost of each of them in terms of number of adders? As Mt M Use multiple adders - E.g. provide one 32-bit adder for each multiplier bi - One input is Multiplicand ANDed with Multiplier bit - The other input is the output of a prior adder - Stack of adders 32 high (time O(n) ) Other possible implementations - Cost/performance trade-off - Organize the 32 additions in a parallel tree Shorter waiting time (log2(n)=log2(32)) - Can even be faster: Smart design: carry save adder Pipelining: many multiplies simultaneously Multiplication Slide 16 Faster Multiplier: parallel tree (hardware) Rather than using a single 32 bit adder 31 times, "unrolls" the loop to use 31 adders and then organizes them (as a tree) to minimize the delay. 64 bit product register - Two pairs of 32-bit registers - Hi: Most-significant 32 bits - Lo: Least-significant 32 bits (Low-order bits) Instructions - mu7t rs, rt : multiply \& put result in Hi& Lo - mu7tu rs, rt : multiply unsigned - mfhi (mflo) rd : move from Hi (Lo) to rd = mu1 rd, rs, rt : put Lo 32 bits of the product in rd Overflow - MIPS "multiply" instructions ignore overflow - Test Hi register to see if the product overflows 32 bits

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts