Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Create a word and the code, put a copy of the paste... the circuit is also a copy of the paste... and the wave can

Create a word and the code, put a copy of the paste... the circuit is also a copy of the paste... and the wave can make a screen, but it should be on the size of the wave, meaning... or you can print it and you will cut it... and arrange them under each other and leave the titles in different colors, as well as the explanation below them

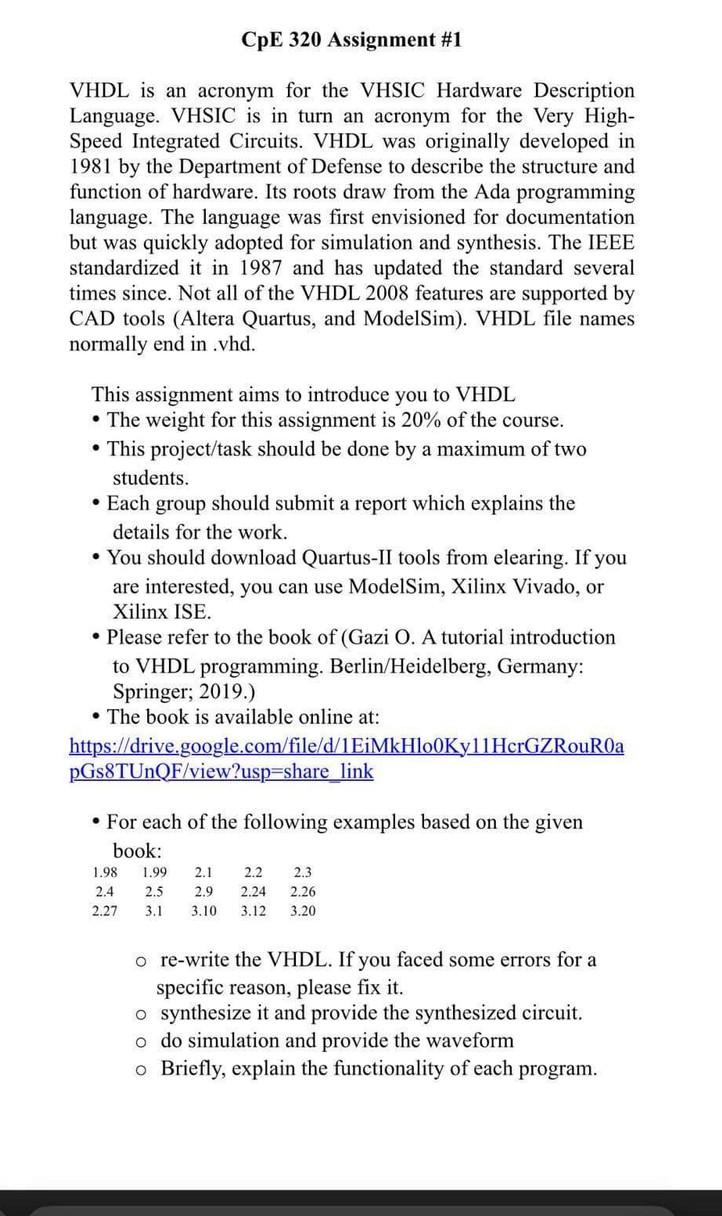

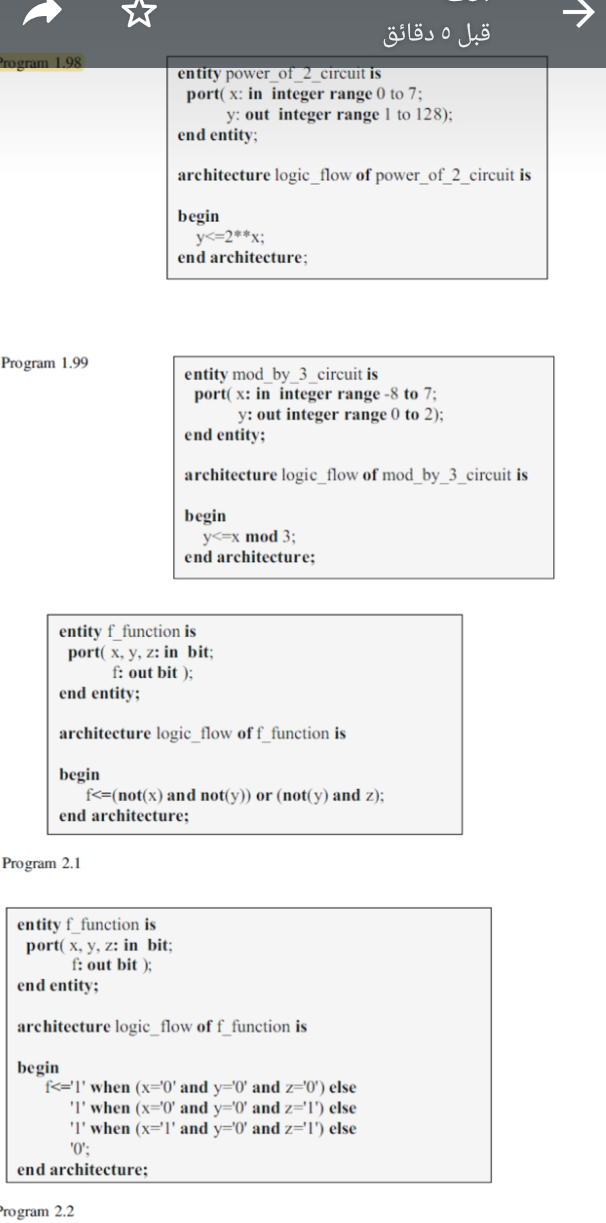

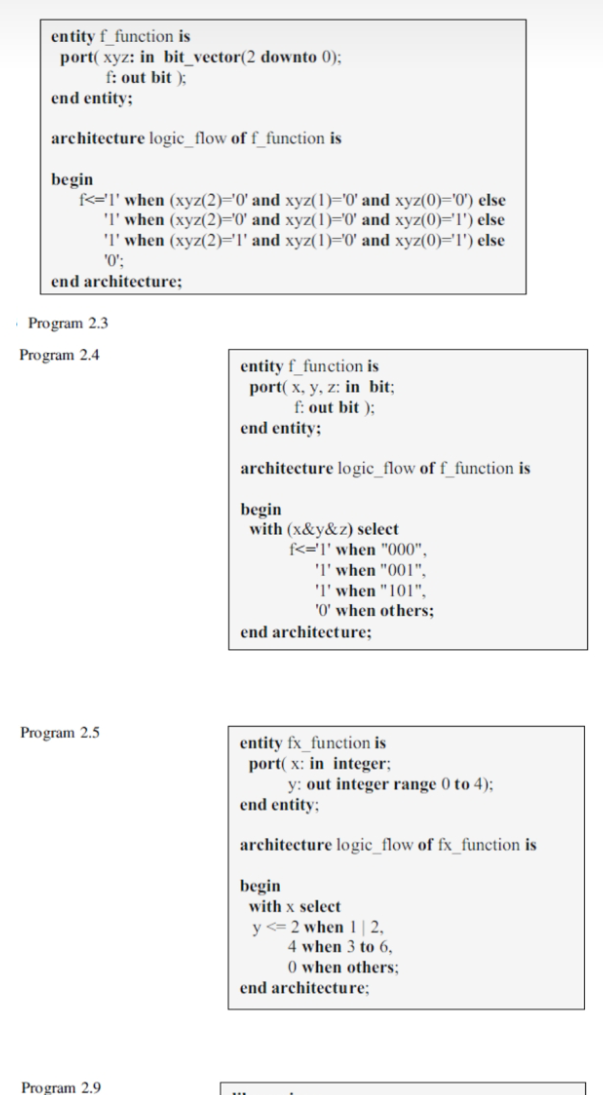

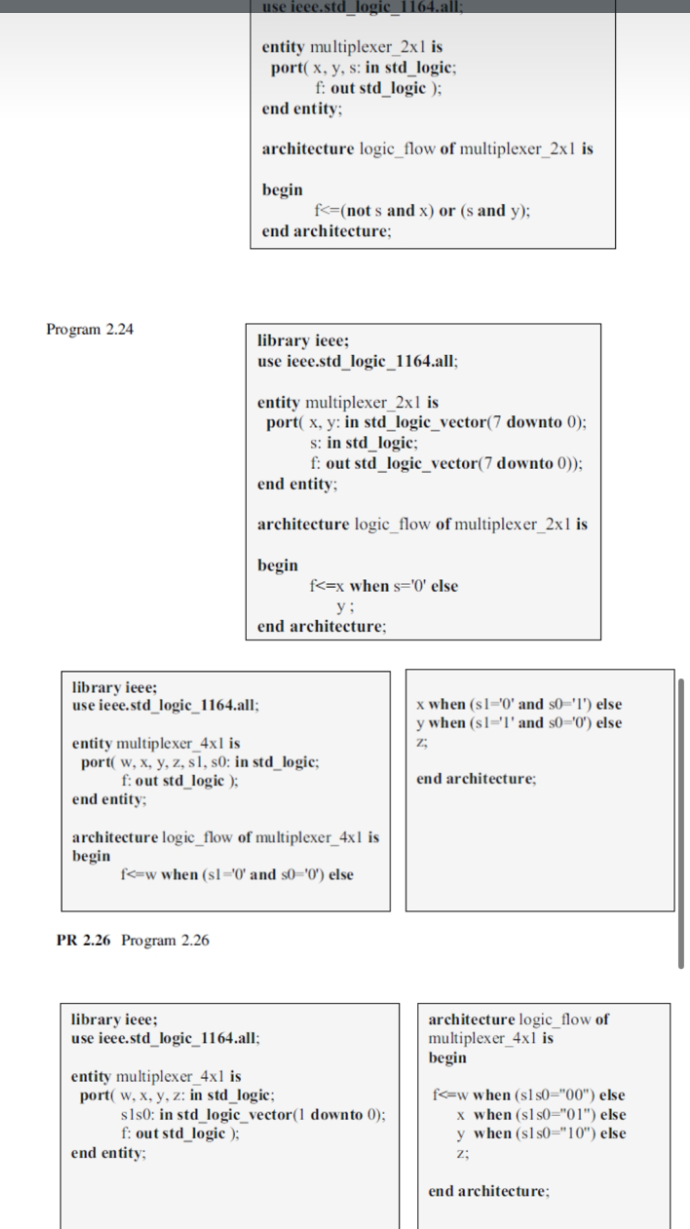

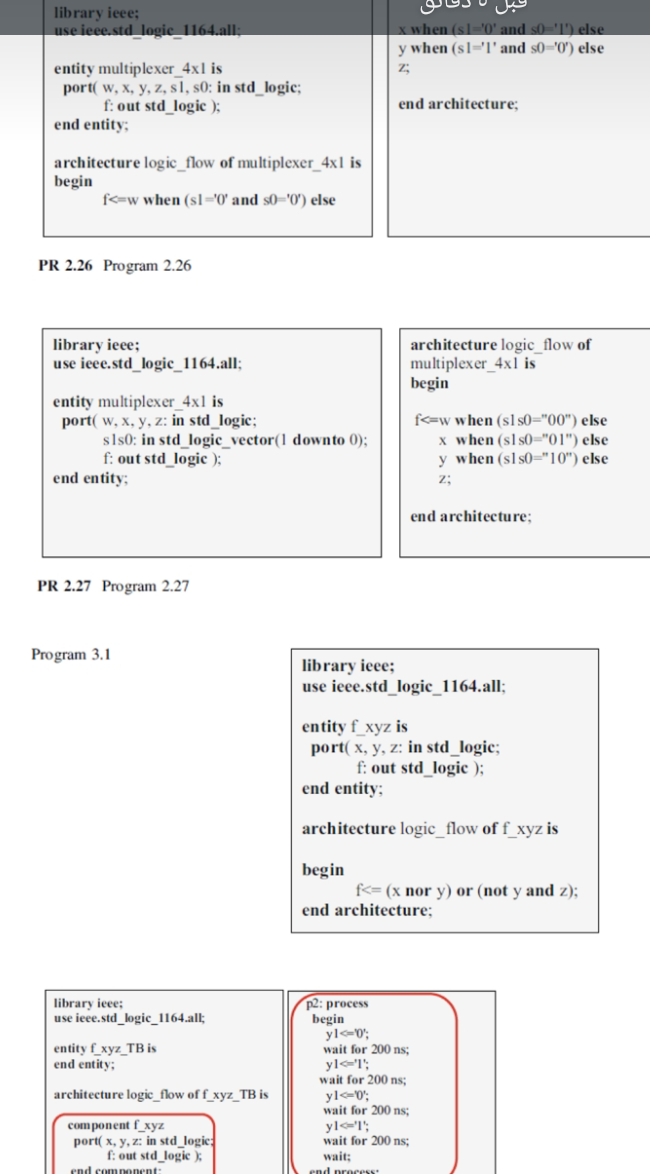

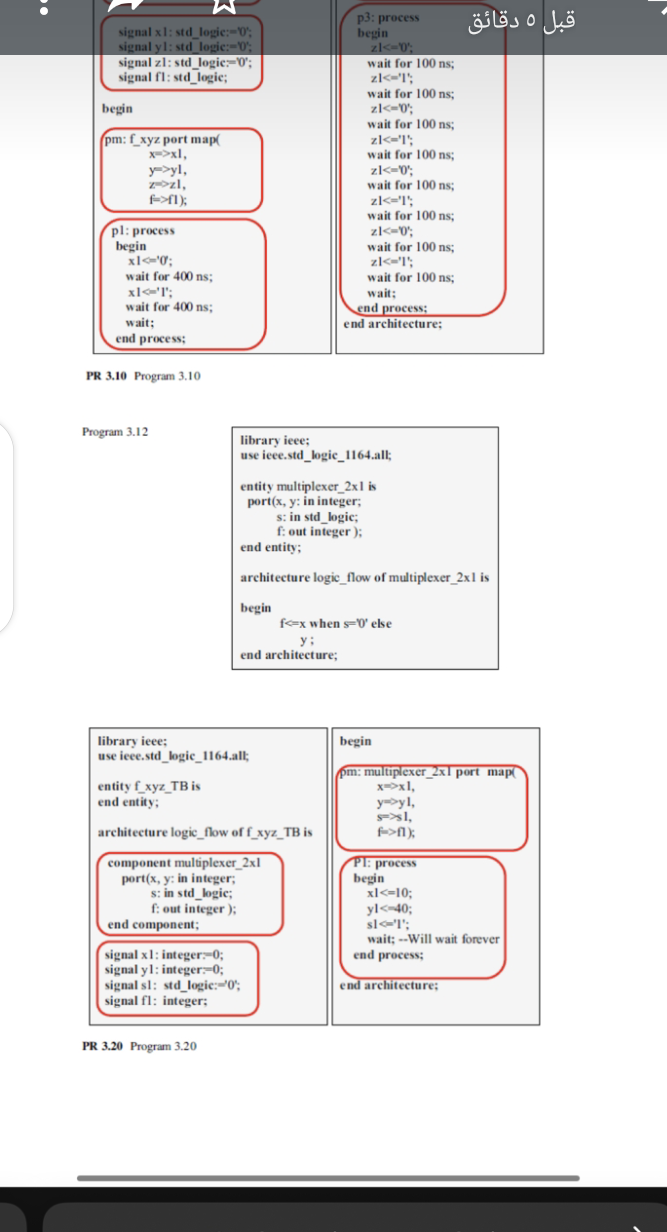

CpE 320 Assignment \#1 VHDL is an acronym for the VHSIC Hardware Description Language. VHSIC is in turn an acronym for the Very HighSpeed Integrated Circuits. VHDL was originally developed in 1981 by the Department of Defense to describe the structure and function of hardware. Its roots draw from the Ada programming language. The language was first envisioned for documentation but was quickly adopted for simulation and synthesis. The IEEE standardized it in 1987 and has updated the standard several times since. Not all of the VHDL 2008 features are supported by CAD tools (Altera Quartus, and ModelSim). VHDL file names normally end in .vhd. This assignment aims to introduce you to VHDL - The weight for this assignment is 20% of the course. - This project/task should be done by a maximum of two students. - Each group should submit a report which explains the details for the work. - You should download Quartus-II tools from elearing. If you are interested, you can use ModelSim, Xilinx Vivado, or Xilinx ISE. - Please refer to the book of (Gazi O. A tutorial introduction to VHDL programming. Berlin/Heidelberg, Germany: Springer; 2019.) - The book is available online at: https://drive.google.com/file/d/1EiMkHlo0Ky11HcrGZRouR0a pGs8TUnQF/view?usp=share link - For each of the following examples based on the given honl. re-write the VHDL. If you faced some errors for a specific reason, please fix it. o synthesize it and provide the synthesized circuit. do simulation and provide the waveform Briefly, explain the functionality of each program. entity power_of_2_circuit is port(x : in integer range 0 to 7 ; y : out integer range 1 to 128); end entity; architecture logic_flow of power_of_2_circuit is begin yStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started