Answered step by step

Verified Expert Solution

Question

1 Approved Answer

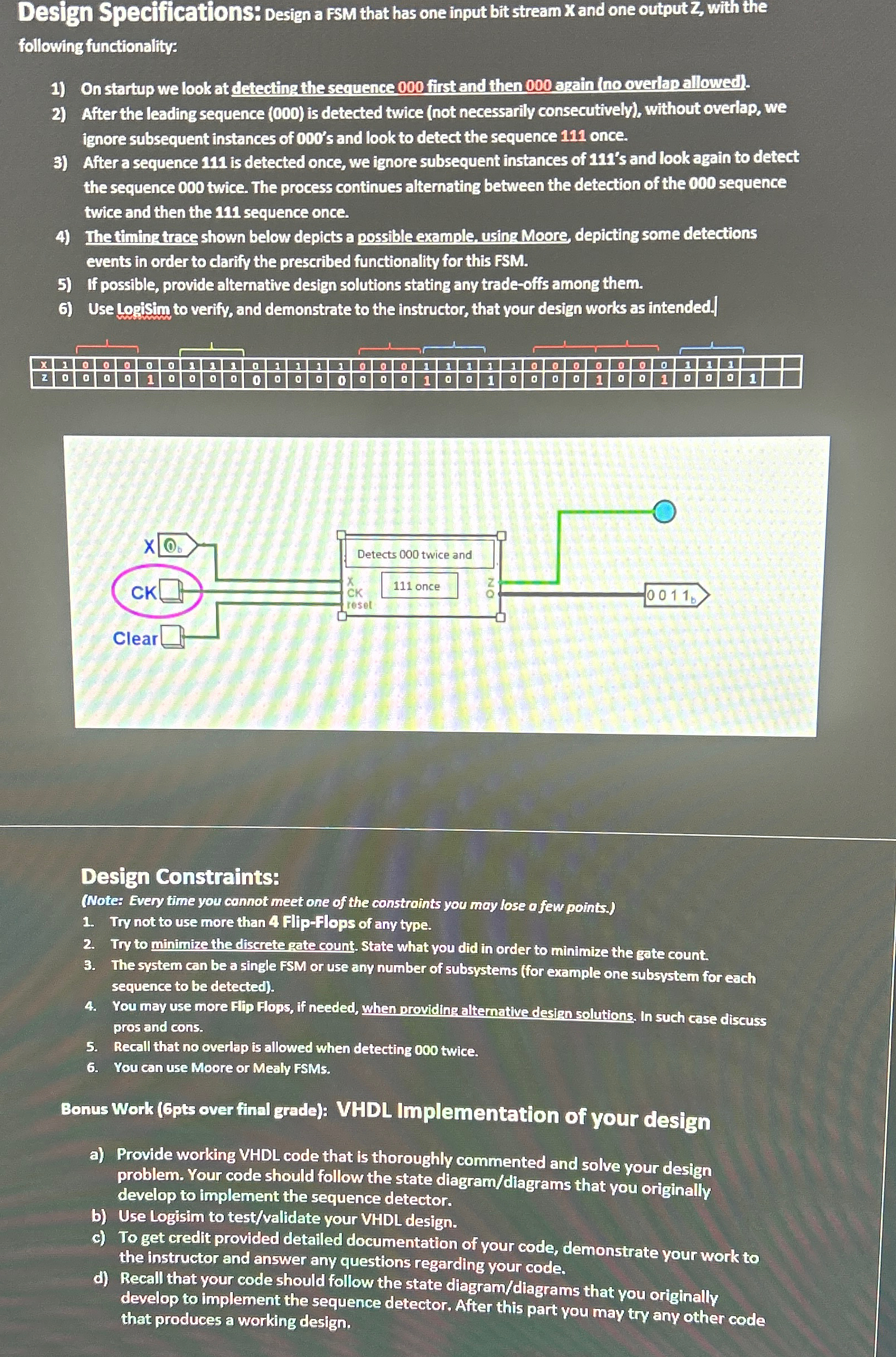

Desfin Speciffeations: Design a FSM that has one input bit stream X and one output Z , with the following functionality: On startup we look

Desfin Speciffeations: Design a FSM that has one input bit stream X and one output with the following functionality:

On startup we look at detecting the seruence first and then again no overlapallowed

After the leading sequence is detected twice not necessarily consecutively without overlap, we ignore subsequent instances of s and look to detect the sequence once.

After a sequence is detected once, we ignore subsequent instances of s and look again to detect the sequence twice. The process continues alternating between the detection of the sequence twice and then the sequence once.

The fimina trace shown below depicts a possible example, usina Moore, depicting some detections events in order to clarify the prescribed functionality for this FSM

If possible, provide alternative design solutions stating any tradeoffis among them.

Use lopistu to verify, and demonstrate to the instructor, that your design works as intended.

tableaaO

Design Constraints:

Wote: Every time you cannot meet one of the constraints you may lose a few points.

Try not to use more than FlipFlops of any type.

Iry to minimize the discreter gate count. State what you did in order to minimize the gate count.

The system can be a single FSM or use any number of subsystems for example one subsystem for each sequence to be detected

You may use more Flip Flops, if needed, when providing altemative desien solutions, In such case discuss pros and cons.

Recall that no overlap is allowed when detecting twice.

You can use Moore or Mealy FEMs.

Bonus Work Gpts over final grade: VHDL Implementation of your design

a Provide working VHDL code that is thoroughly commented and solve your design problem. Your code should follow the state diagramdiagrams that you originally develop to implement the sequence detector.

b Use Logisim to testvalidate your VHDL design.

c To get credit provided detailed documentation of your code, demonstrate your work to the instructor and answer any questions regarding your code.

d Recall that your code should follow the state diagramdiagrams that you originally develop to implement the sequence detector. After this part you may try any other code that produces a working design.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started