Answered step by step

Verified Expert Solution

Question

1 Approved Answer

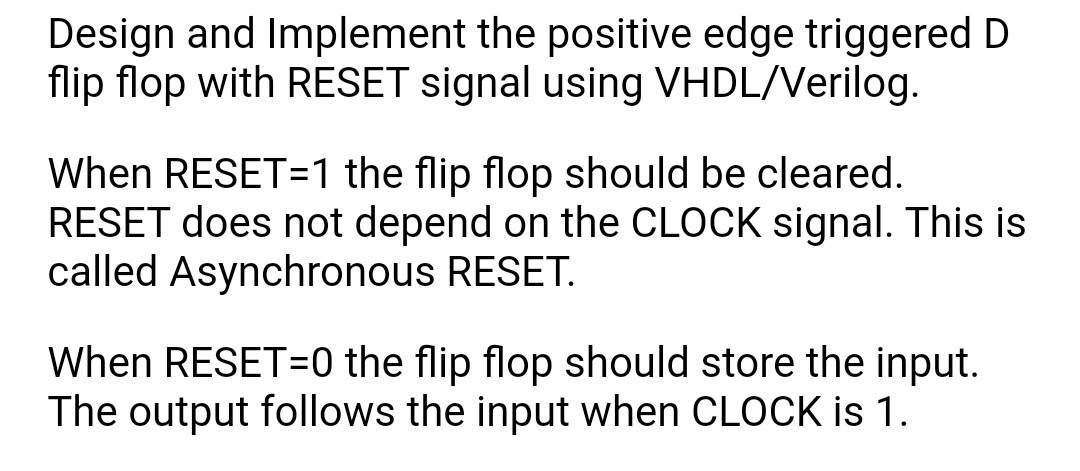

Design and Implement the positive edge triggered D flip flop with RESET signal using VHDL/Verilog. When RESET=1 the flip flop should be cleared. RESET does

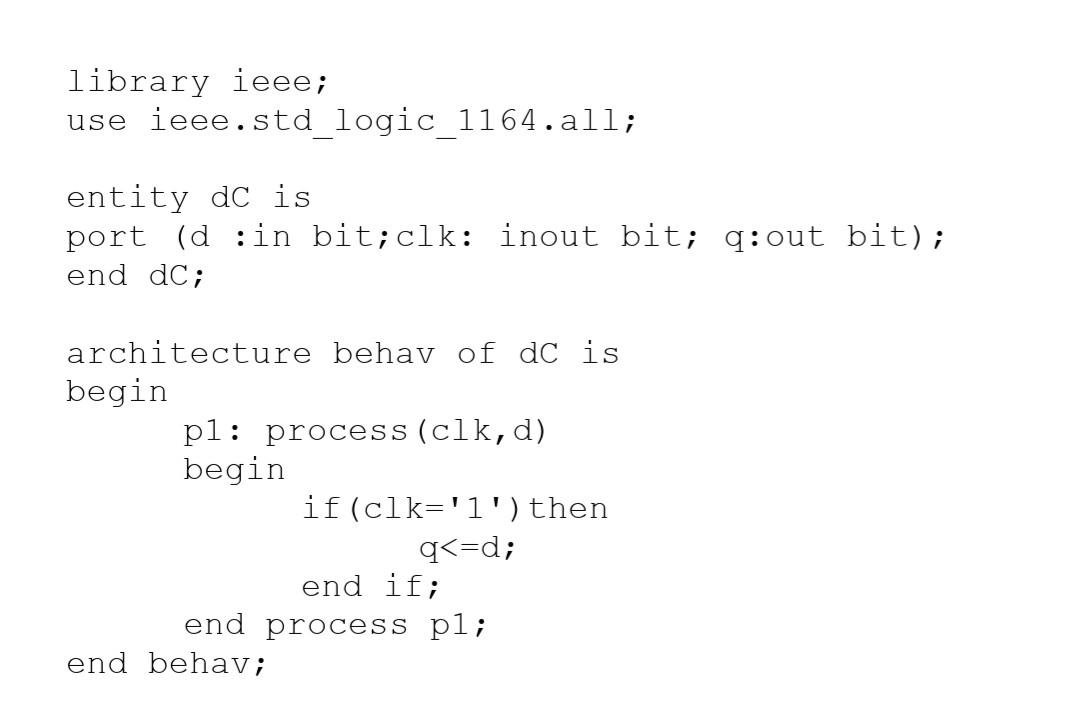

Design and Implement the positive edge triggered D flip flop with RESET signal using VHDL/Verilog. When RESET=1 the flip flop should be cleared. RESET does not depend on the CLOCK signal. This is called Asynchronous RESET. When RESET=0 the flip flop should store the input. The output follows the input when CLOCK is 1. The Demo program implements the regular D flip flop operation without the RESET signal. Demo Program: file2.vhd Demo Program as text file: Demo Lab5 Fall2020.txt Lab report template: Lab 5 Template VHD spring 2021.doc library ieee; use ieee.std logic 1164.all; entity dC is port (d :in bit;clk: inout bit; q:out bit); end dC; architecture behav of dC is begin pl: process (clk, d) begin if(clk='1') then q

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started