Question

DONT COPY OTHER SOLUTIONS General Description : You are to create an 8-to-1 MUX using 7 instances of the Xilinx 2-to-1 MUX module named (M2_1)

DONT COPY OTHER SOLUTIONS

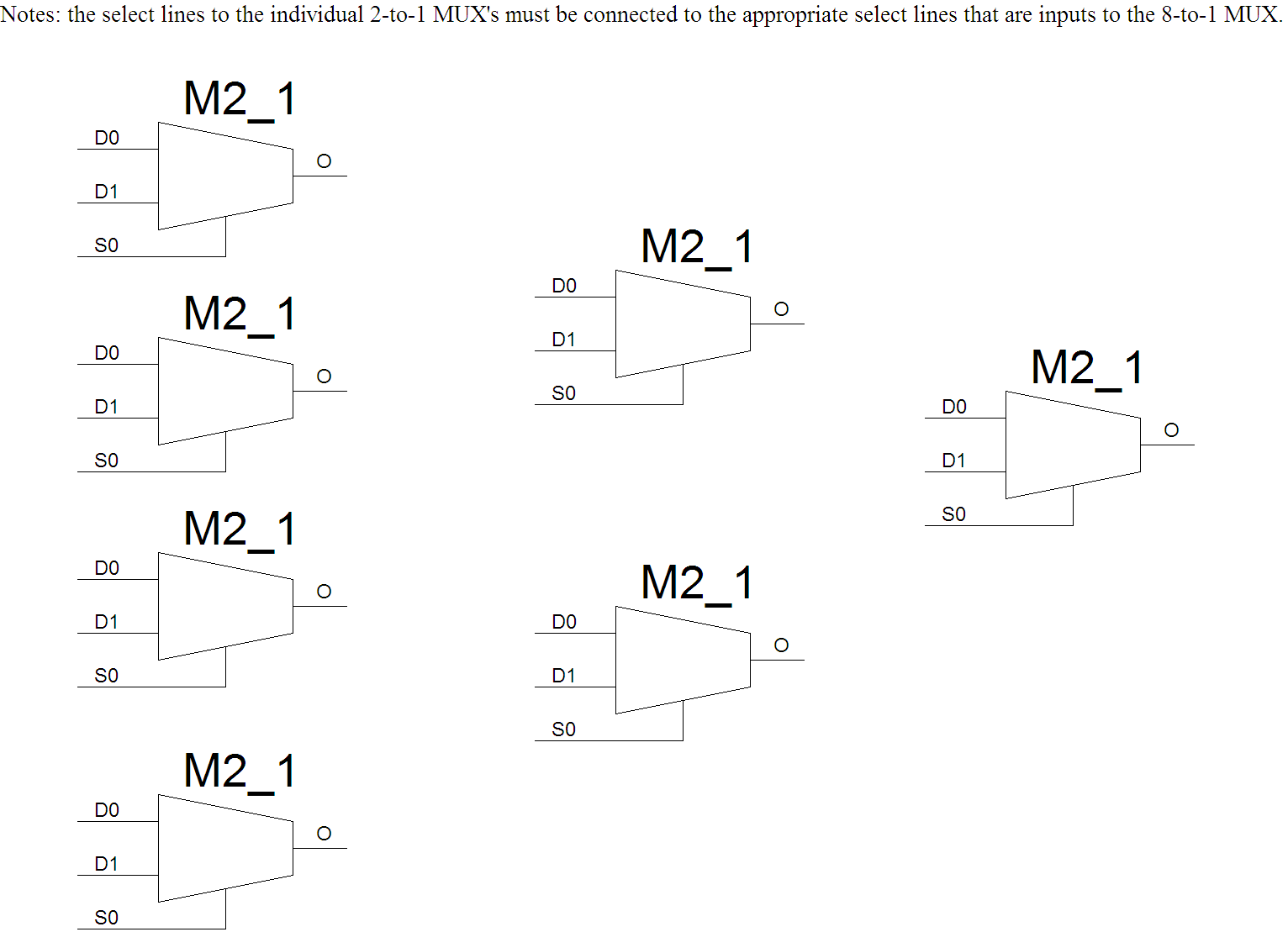

General Description: You are to create an 8-to-1 MUX using 7 instances of the Xilinx 2-to-1 MUX module named (M2_1) in the library of parts. You design will have eight data inputs, one bit each (d7d0). There will be one output, also being 1-bit (y). The MUX is to be created using ONLY 2-to-1 MUXs, having two data inputs (one bit each) and one output, also being 1-bit. The purpose of this lab is to use structural modeling techniques with the schematic editor. The unconnected structure of the 8-to-1 MUX is shown in the diagram below:

Based on the information and diagram, provide verilog testbench code

Notes: the select lines to the individual 2-to-1 MUX's must be connected to the appropriate select lines that are inputs to the 8-to-1 MUX M2 1 DO D1 SO M2 1 DO D1 SO M2 1 M2 1 DO D1 SO DO D1 SO M2 1 M2 1 DO D1 SO DO D1 SO M2 1 DO D1 SO Notes: the select lines to the individual 2-to-1 MUX's must be connected to the appropriate select lines that are inputs to the 8-to-1 MUX M2 1 DO D1 SO M2 1 DO D1 SO M2 1 M2 1 DO D1 SO DO D1 SO M2 1 M2 1 DO D1 SO DO D1 SO M2 1 DO D1 SOStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started