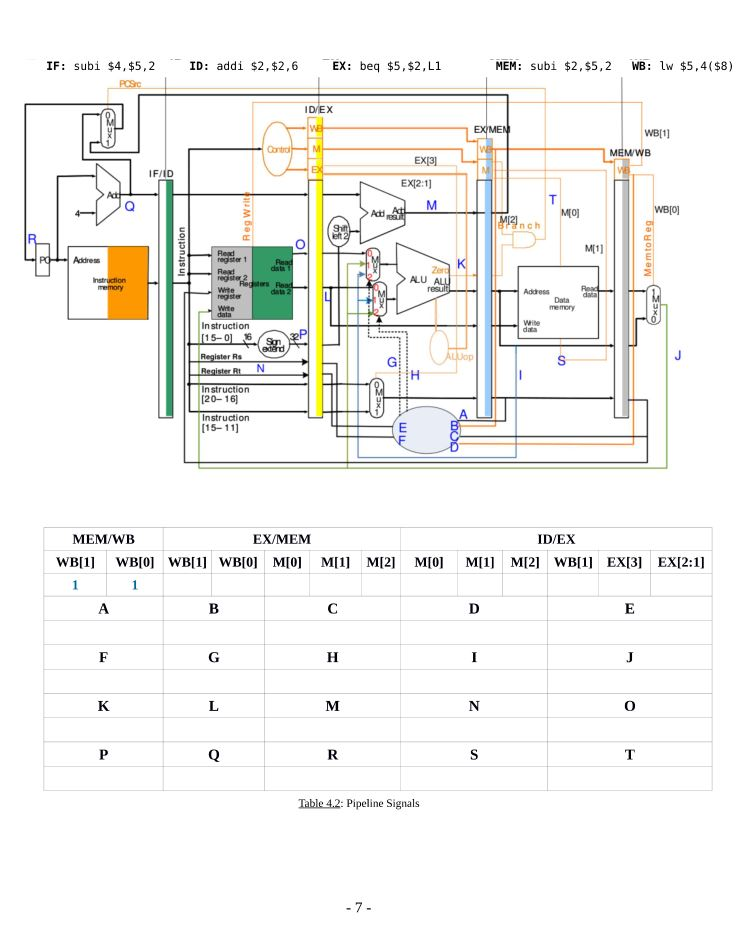

Fill in the blanks of Table 4.2. There are five input signals going into the forwarding unit and two output signals generated by the forwarding unit. Fill in the data signals that go into the ALU.

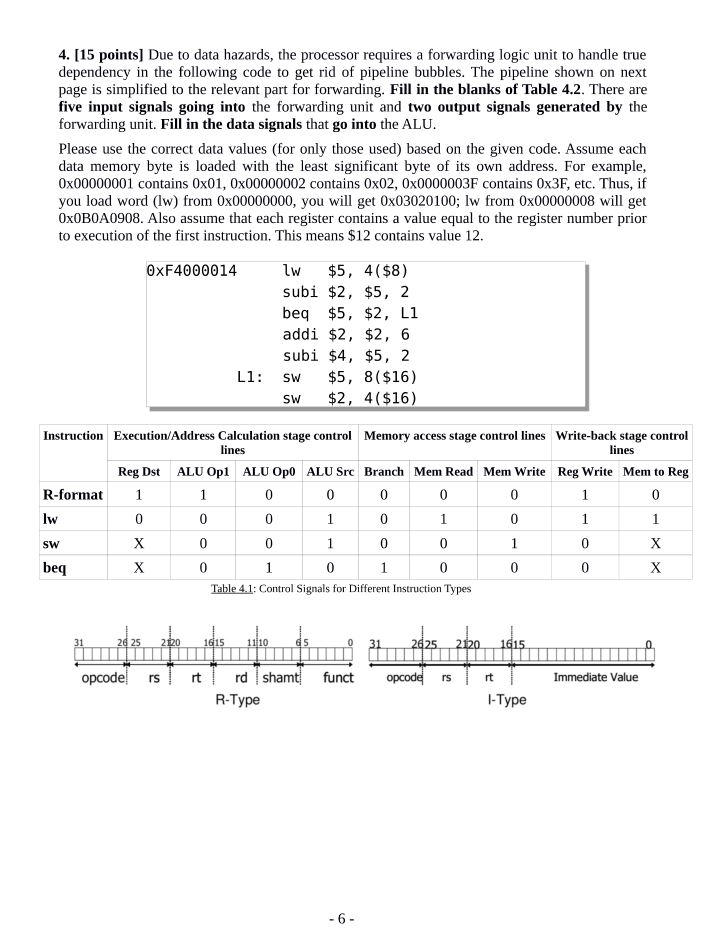

4. [15 points] Due to data hazards, the processor requires a forwarding logic unit to handle true dependency in the following code to get rid of pipeline bubbles. The pipeline shown on next page is simplified to the relevant part for forwarding. Fill in the blanks of Table 4.2. There are five input signals going into the forwarding unit and two output signals generated by the forwarding unit. Fill in the data signals that go into the ALU. Please use the correct data values (for only those used) based on the given code. Assume each data memory byte is loaded with the least significant byte of its own address. For example, 0x00000001 contains 0x01, 0x00000002 contains 0x02, 0x0000003F contains 0x3F, etc. Thus, if you load word (lw) from 0x00000000, you will get 0x03020100; lw from 0x00000008 will get 0x0B0A0908. Also assume that each register contains a value equal to the register number prior to execution of the first instruction. This means $12 contains value 12. 0xF4000014 lw $5, 4 ($8) subi $2, $5, 2 beq $5, $2, L1 addi $2, $22, 6 subi $4, $5, 2 L1 SW $5 8 ($16) SW $2, 4 ($16) Instruction Execution/Address Calculation stage control Memory access stage control lines write-back stage control lines lines Reg Dst ALU opl ALU opo ALU Src Branch Mem Read Mem Write Reg Write Mem to Reg R-format 1 1 0 0 0 0 1 0 Table 41: Control Signals for Different Instruction Types 31 1615 1110 opcode rs rt rd sham funct opcod rs rt Immediate Value R-Type I-Type 4. [15 points] Due to data hazards, the processor requires a forwarding logic unit to handle true dependency in the following code to get rid of pipeline bubbles. The pipeline shown on next page is simplified to the relevant part for forwarding. Fill in the blanks of Table 4.2. There are five input signals going into the forwarding unit and two output signals generated by the forwarding unit. Fill in the data signals that go into the ALU. Please use the correct data values (for only those used) based on the given code. Assume each data memory byte is loaded with the least significant byte of its own address. For example, 0x00000001 contains 0x01, 0x00000002 contains 0x02, 0x0000003F contains 0x3F, etc. Thus, if you load word (lw) from 0x00000000, you will get 0x03020100; lw from 0x00000008 will get 0x0B0A0908. Also assume that each register contains a value equal to the register number prior to execution of the first instruction. This means $12 contains value 12. 0xF4000014 lw $5, 4 ($8) subi $2, $5, 2 beq $5, $2, L1 addi $2, $22, 6 subi $4, $5, 2 L1 SW $5 8 ($16) SW $2, 4 ($16) Instruction Execution/Address Calculation stage control Memory access stage control lines write-back stage control lines lines Reg Dst ALU opl ALU opo ALU Src Branch Mem Read Mem Write Reg Write Mem to Reg R-format 1 1 0 0 0 0 1 0 Table 41: Control Signals for Different Instruction Types 31 1615 1110 opcode rs rt rd sham funct opcod rs rt Immediate Value R-Type I-Type