Question

Hello I'm suppose to write an IA32 assembly routine using gnu assemly. The assembly program should implement a function with the prototype: unsigned char check_cache(line

Hello I'm suppose to write an IA32 assembly routine using gnu assemly. The assembly program should implement a function with the prototype:

unsigned char check_cache(line cache[4], unsigned char addr);

This function will check whether the given cache stores the data at the given memory address. If the cache stores the data at the given memory address (i.e., cache hit), thn the function will return the sotred data, else this funciton will return 0xFF (i.e., cache miss). The important assumptions about the function are as follows.

-Memory addresses are 8 bits wide (m=8). Therefore, we use unsigned char to store memory addresses.

-Memory accesses are to 1-byte words (not to 4-byte words). Therefore, the return type of the function is unsigned char.

-The cache is directed-mapped (E=1), with a 4-byte block size (B=4) and four sets (S=4).

-A cache line is defined using struct as follows. valid can store only 0 or 1. If the number of tag bits (i.e., t) is less than 8 bits (the size of char), t low-order bits of tag will be used to store the tag bits, and the unused bits will be zero.

-Cache block don't store byte data 0xFF because it is used for indicating cache miss in this function.

(Also, when writing the code for the assembly program, please provide comments explaining what each line of code does.)

When modifying any callee-save register, please save and restore its old value.

The following steps should help get you started:

1. Find the number of tag bits, the number of set index bits, and the number of block offset bits using the given information above.

2. The given memory address must be stroed in a byte-sized register and then split the address into three components (set index bits, tag bits, and block offset bits). The recommended bit-level operations to use are andb and shrb and 1-byte move instruction movb to split the address. Each component's value can be checked by putting it in the register used for storing return values (e.g., %al for 1-byte return values) before moving onto the next steps.

3. Find the start address of the corresponding cache set using the set index bits. To find the start address, use the size of struct line, and multiplication instructions can be used.

4. Read the valid bit from the cache set using movb. If the valid bit has 0 (i.e., cache miss), store 0xFF in the return register and finish the function. If the valid bit has 1, move onto the next step. It is also recommended to use testb for this comparison.

5. Read the tag bits from the cache set using movb and then compare them with the tag bits in the memory address. If they are not the same (i.e., cache mis), store 0xFF in the return register and finish the function. Otherwise (i.e., cache hit), move onto the next step. You maywant to use cmpb for this comparison.

6. Read one byte from the cache block using the block offset bits and then put it in the return register. Also, %al needs to be used once again for 1-byte return values.

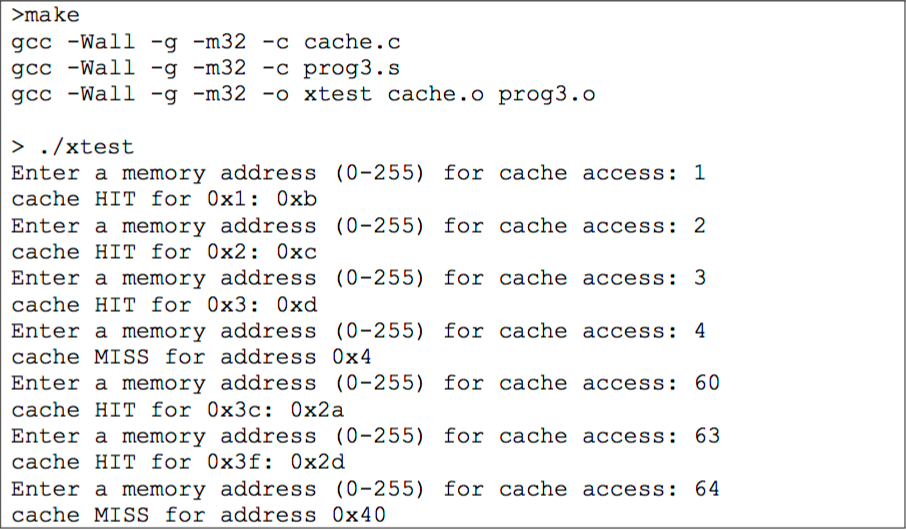

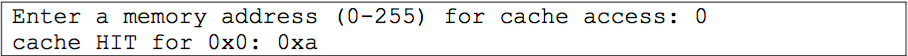

The way the program should run once finished is shown below.

----------------------------------------------------------

To make things simpler, I will also provided the C code the program is based off of the assembly code it's running off of, a guide on what to use for IA32 assembly, and the starter IA32 assembly program that needs to be modified for this task. Thanks.

---------------------------------------------------------

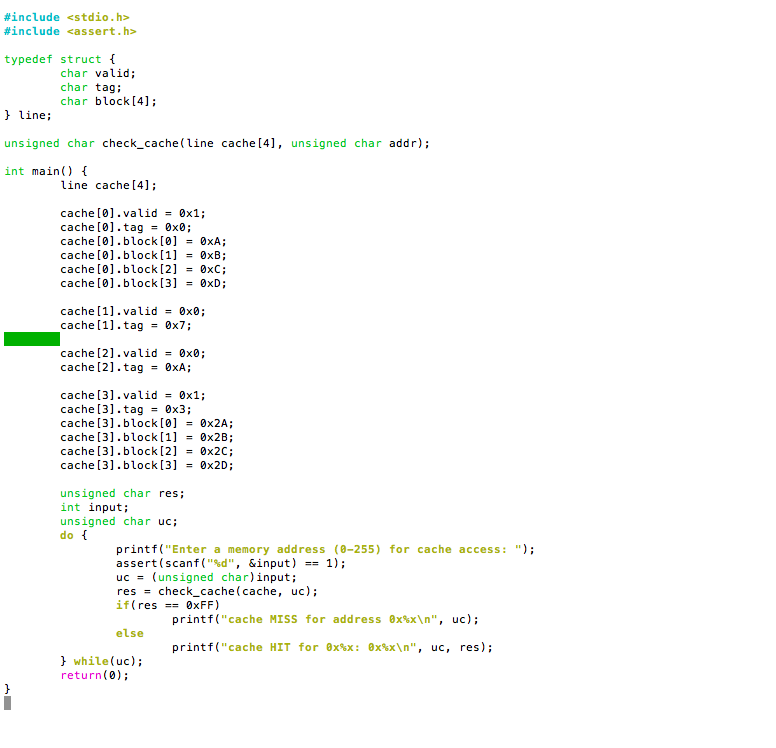

C code (don't modify)

------------------------------

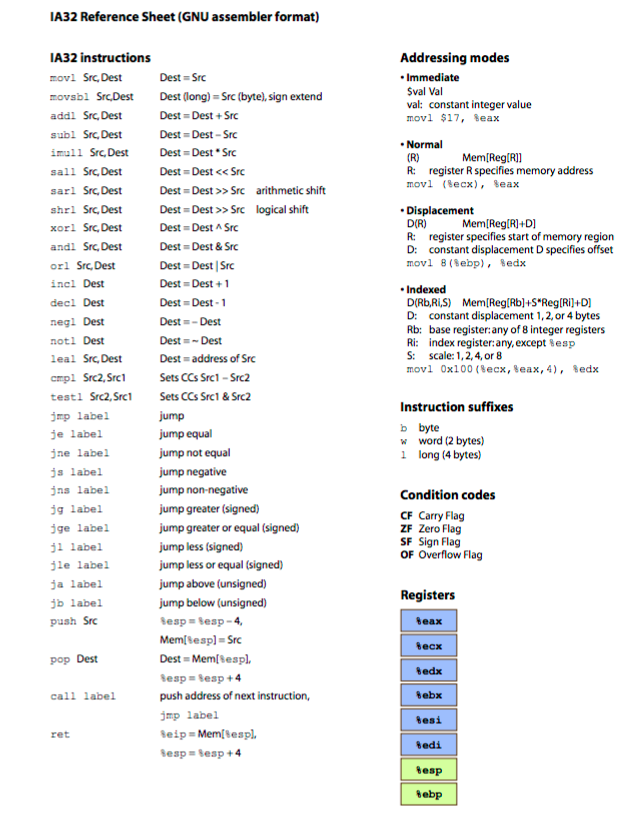

IA32 Guide

---------------------------------------

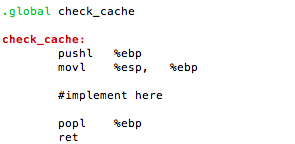

IA32 Assembly starter code that needs modifications

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started