Answered step by step

Verified Expert Solution

Question

1 Approved Answer

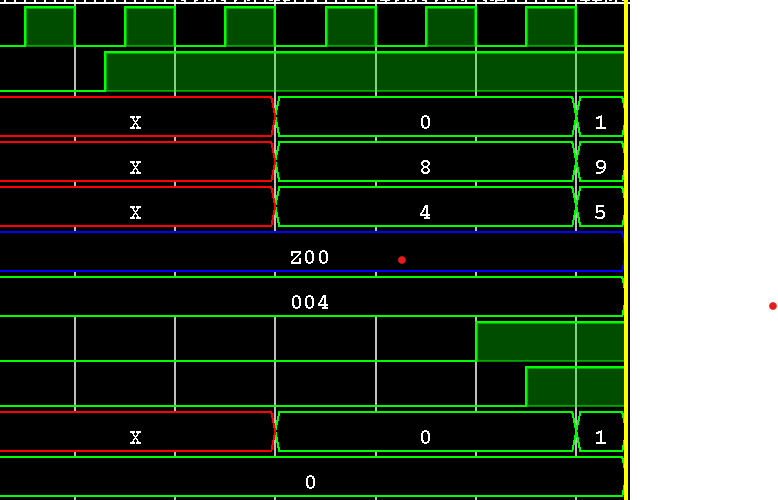

Here is my verilog code and the testbench code however there is an issue with my waveform not being accurate can you please find the

Here is my verilog code and the testbench code however there is an issue with my waveform not being accurate can you please find the issue and explain why?

module line

input wire rstn Active low reset

input wire clk Clock

input wire signed : m Signed input

input wire signed : x Signed input

input wire signed : c Signed input

input wire validin Inputs valid

output reg signed : y Signed output

output reg yvalid Y valid, driven by design

;

reg signed : productreg; Pipeline register for product

reg signed : sumreg; Pipeline register for sum

Stage : Multiplier pipeline stage

always @posedge clk or negedge rstn begin

if rstn

productreg b; Reset product register

else if validin

productreg m x; Calculate product

end

Stage : Adder pipeline stage

always @posedge clk or negedge rstn begin

if rstn

sumreg b; Reset sum register

else if validin

sumreg productreg c; Calculate sum

end

Output and valid signal assignment

always @posedge clk or negedge rstn begin

if rstn begin

y b; Reset output

yvalid b; Reset valid signal

end

else if validin begin

y sumreg; Assign output

yvalid b; Set valid signal

endmodule tbline

;

reg clk;

reg rstn;

wire signed : m;

wire signed : x;

wire signed : c;

wire signed : y;

wire signed : tby;

reg validin;

wire yvalid;

reg : addrin addry;

line dut ;

rom #addrwidth datawidth initfilemdat"

mmem

addraddrin

data m

;

rom #addrwidth datawidth initfilexdat"

xmem

addraddrin

data x

;

rom #addrwidth datawidth initfilecdat"

cmem

addraddrin

data c

;

rom #addrwidth datawidth initfileydat"

ymem

addraddry

data tby

;

always # clk ~clk;

integer filehandle;

initial

begin

filehandle $fopenoutputtxtw;

clk ;

rstn h;

validin ;

# rstn h;

#;

addrin h;

#;

validin ;

for integer i ; i ; i i

begin

#;

assert y tby;

addrin addrin ;

end

validin ;

#;

$fclosefilehandle;

end

alwaysff @ posedge clk

begin

if rstn

begin

addry #h;

end

else if yvalid

begin

$fwritefilehandle, b

y;

assert y tby

else $fataly not equal to tby;

addry # addry ;

end

end

endmodule

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started