Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Hi! Please help me with this problem. I have the truth table and K-map done (I think), and I am having the biggest issue on

Hi! Please help me with this problem. I have the truth table and K-map done (I think), and I am having the biggest issue on how to write this in code from the table. Thank you!

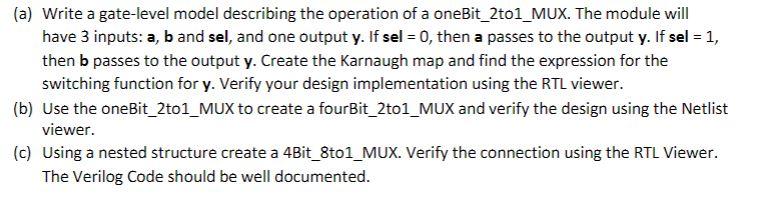

(a) Write a gate-level model describing the operation of a oneBit_2t01_MUX. The module will have 3 inputs: a, b and sel, and one output y. If sel = 0, then a passes to the output y. If sel = 1, then b passes to the output y. Create the Karnaugh map and find the expression for the switching function for y. Verify your design implementation using the RTL viewer. (b) Use the oneBit_2t01_MUX to create a fourBit_2t01_MUX and verify the design using the Netlist viewer. (c) Using a nested structure create a 4Bit_8to1_MUX. Verify the connection using the RTL Viewer. The Verilog Code should be well documentedStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started