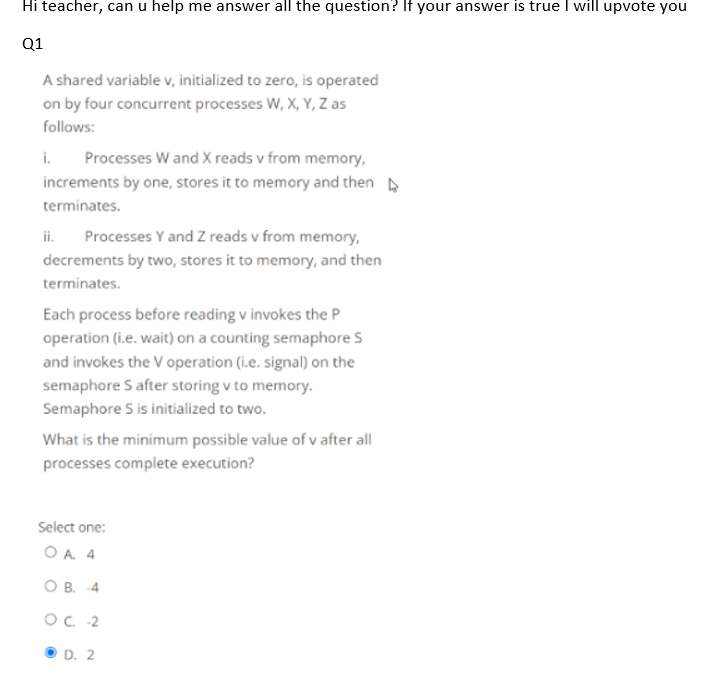

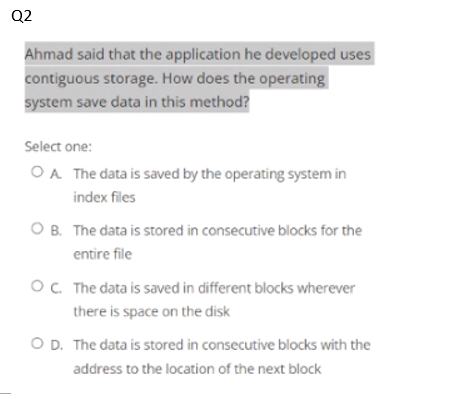

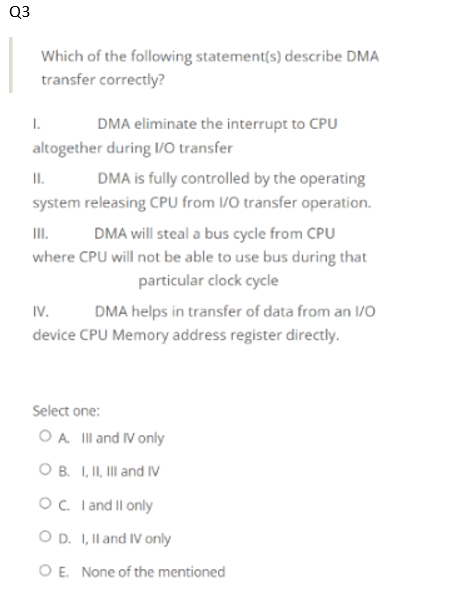

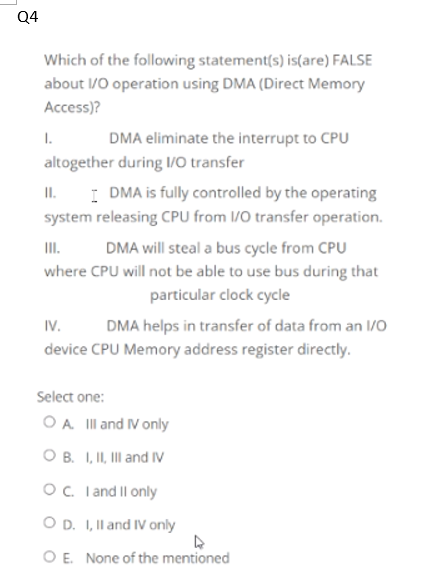

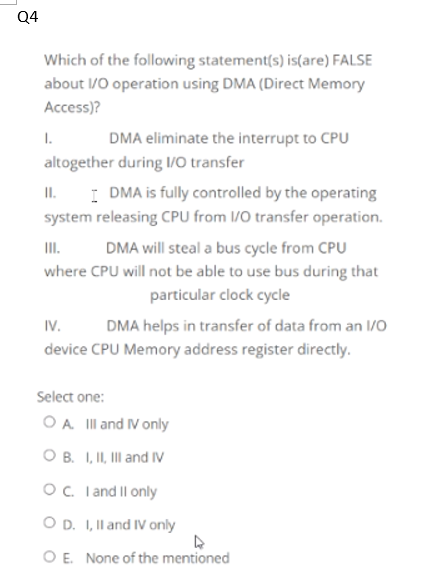

Hi teacher, can u help me answer all the question? If your answer is true I will upvote you Q1 A shared variable v, initialized to zero, is operated on by four concurrent processes W, X, Y, Z as follows: i. Processes Wand X reads v from memory, increments by one, stores it to memory and then A terminates. ii. Processes Y and Z reads y from memory, decrements by two, stores it to memory, and then terminates. Each process before reading v invokes the P operation (i.e. wait) on a counting semaphore 5 and invokes the V operation (i.e. signal) on the semaphore S after storing v to memory. Semaphore S is initialized to two. What is the minimum possible value of v after all processes complete execution? Select one: O A 4 OB. 4 OC -2 D. 2 Q2 Ahmad said that the application he developed uses contiguous storage. How does the operating system save data in this method? Select one: O A The data is saved by the operating system in index files OB. The data is stored in consecutive blocks for the entire file OC The data is saved in different blocks wherever there is space on the disk OD. The data is stored in consecutive blocks with the address to the location of the next block Q3 Which of the following statement(s) describe DMA transfer correctly? 1. DMA eliminate the interrupt to CPU altogether during 1/0 transfer II. DMA is fully controlled by the operating system releasing CPU from 1/0 transfer operation. III. DMA will steal a bus cycle from CPU where CPU will not be able to use bus during that particular clock cycle IV. DMA helps in transfer of data from an 1/0 device CPU Memory address register directly. Select one: O A Illand IV only OB. I, II, III and IV OC I and II only OD. I, II and IV only O E. None of the mentioned Q4 Which of the following statement(s) is(are) FALSE about 1/0 operation using DMA (Direct Memory Access)? 1. DMA eliminate the interrupt to CPU altogether during I/O transfer II. I DMA is fully controlled by the operating system releasing CPU from 1/0 transfer operation. III. DMA will steal a bus cycle from CPU where CPU will not be able to use bus during that particular clock cycle DMA helps in transfer of data from an 1/0 device CPU Memory address register directly. IV. Select one: OA II and IV only OB. 1, 11, III and IV OC I and II only OD. I, II and IV only OE. None of the mentioned