Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Hi this is from my computer architecture class. Look not easy. Question 1 General a. (5 marks) What is the average cycles per instruction (CPI)

Hi this is from my computer architecture class. Look not easy.

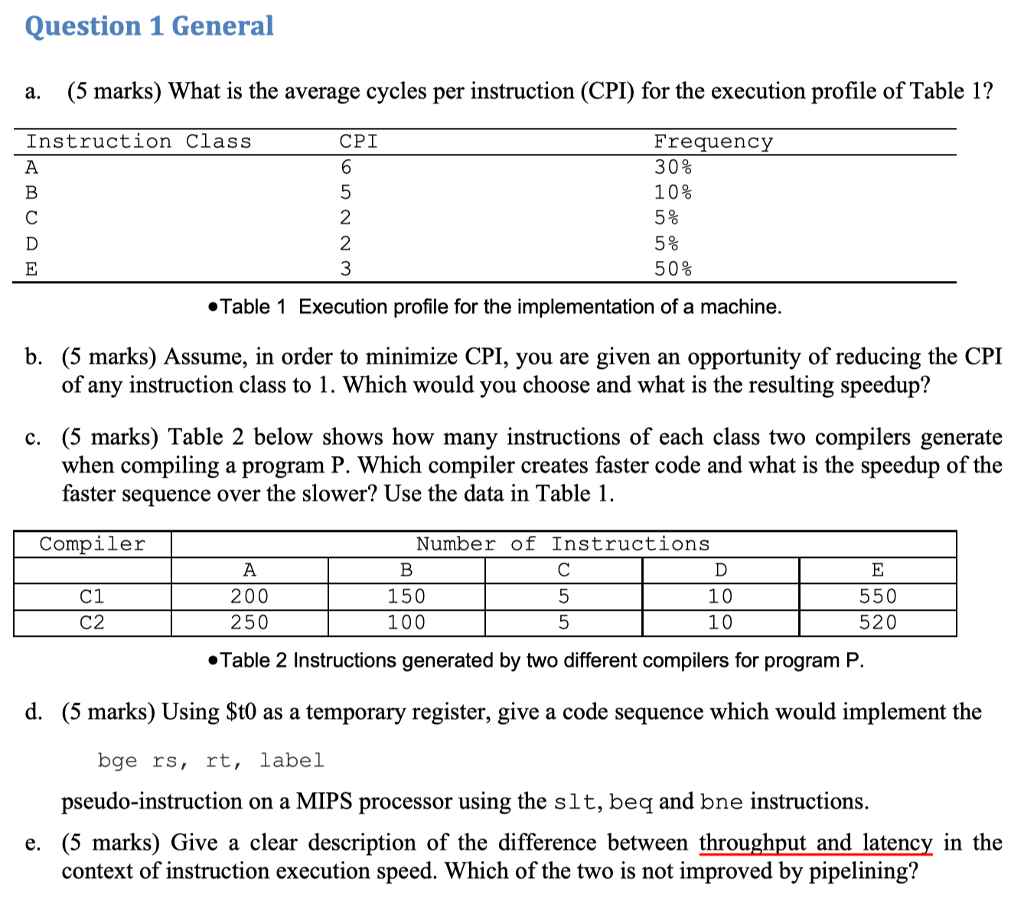

Question 1 General a. (5 marks) What is the average cycles per instruction (CPI) for the execution profile of Table 1? Instruction Class CPI Frequency 30% 10% 58 5% 50% 2 2 Table 1 Execution profile for the implementation of a machine. b. (5 marks) Assume, in order to minimize CPI, you are given an opportunity of reducing the CPI of any instruction class to 1. Which would you choose and what is the resulting speedup? C. (5 marks) Table 2 below shows how many instructions of each class two compilers generate when compiling a program P. Which compiler creates faster code and what is the speedup of the faster sequence over the slower? Use the data in Table 1 Compiler Number of Instructions C1 C2 200 250 150 100 10 10 550 520 Table 2 Instructions generated by two different compilers for program P. d. (5 marks) Using $t0 as a temporary register, give a code sequence which would implement the bge rs, rt, label pseudo-instruction on a MIPS processor using the slt, beq and bne instructions. e. (5 marks) Give a clear description of the difference between throughput and latency in the context of instruction execution speed. Which of the two is not improved by pipelining? Question 1 General a. (5 marks) What is the average cycles per instruction (CPI) for the execution profile of Table 1? Instruction Class CPI Frequency 30% 10% 58 5% 50% 2 2 Table 1 Execution profile for the implementation of a machine. b. (5 marks) Assume, in order to minimize CPI, you are given an opportunity of reducing the CPI of any instruction class to 1. Which would you choose and what is the resulting speedup? C. (5 marks) Table 2 below shows how many instructions of each class two compilers generate when compiling a program P. Which compiler creates faster code and what is the speedup of the faster sequence over the slower? Use the data in Table 1 Compiler Number of Instructions C1 C2 200 250 150 100 10 10 550 520 Table 2 Instructions generated by two different compilers for program P. d. (5 marks) Using $t0 as a temporary register, give a code sequence which would implement the bge rs, rt, label pseudo-instruction on a MIPS processor using the slt, beq and bne instructions. e. (5 marks) Give a clear description of the difference between throughput and latency in the context of instruction execution speed. Which of the two is not improved by pipelining

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started