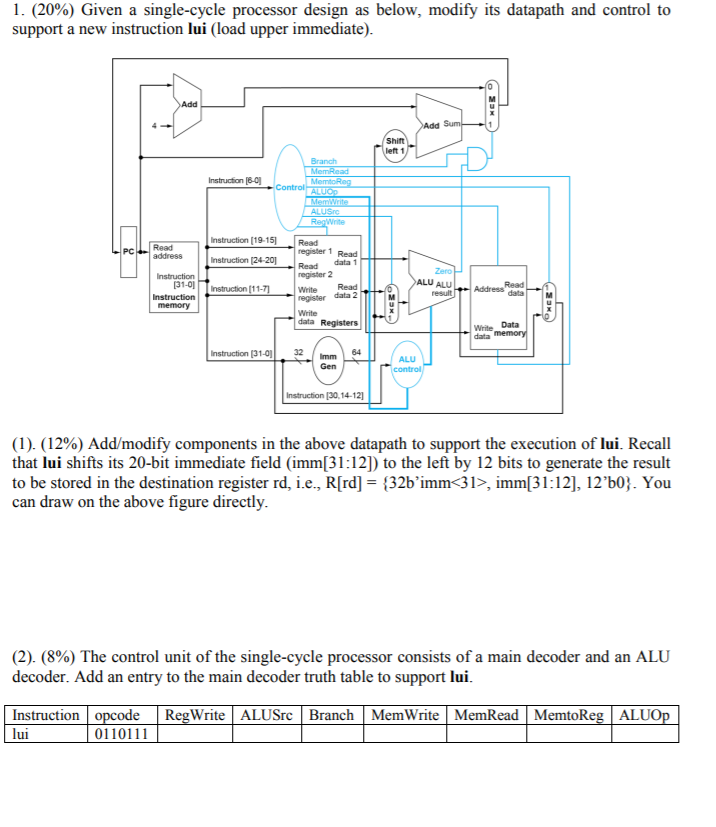

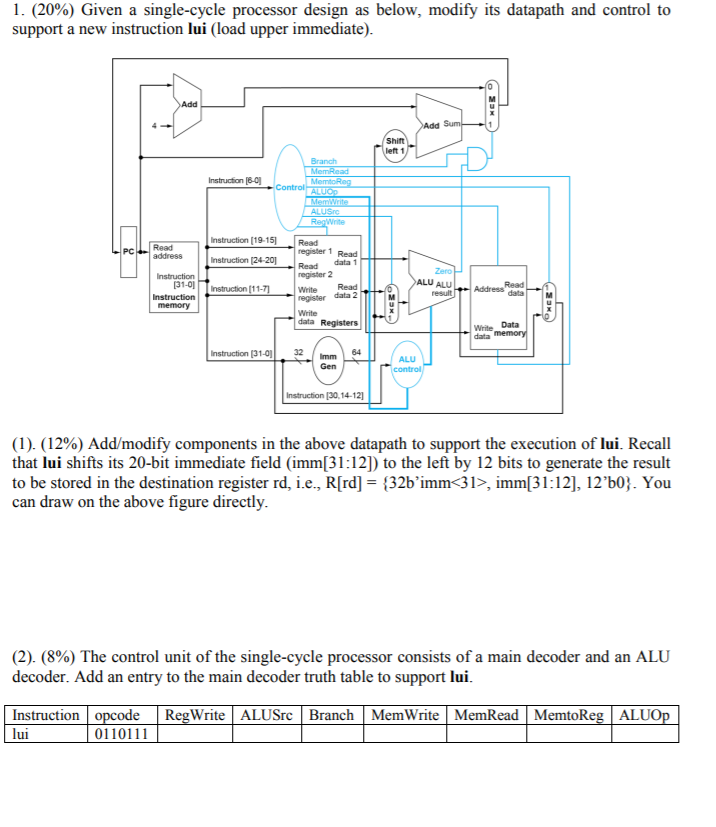

I. (2006) Given a single-cycle processor design as below, modify its datapath and control to support a new instruction lui (load upper immediate) MI Shift eft 1 Branch Instruction 16-0 ALUSrc Instruction (19-15Read PCaddress Read register 1 Read instruction 124-20Read data 1 Zero register 2 Write Read register data 2 Write data Registers 31-01 Instruction AL Addressdata M Write Data mm84 Gen Instruction (31-0 32 ALU Instruction [30,14-121 (1). (12%) Add/modify components in the above datapath to support the execution of lui. Recall that lui shifts its 20-bit immediate field (imm[31:12] to the left by 12 bits to generate the result to be stored in the destination register rd, i.e., R[rd32b'imm, imm[31:12], 12'b0;. You can draw on the above figure directly (2), (800) The control unit of the single-cycle processor consists of a main decoder and an ALU decoder. Add an entry to the main decoder truth table to support lui Instruction opcode RegWrite ALUSrc Branch MemWrite MemRead MemtoR AL ull 0110111 I. (2006) Given a single-cycle processor design as below, modify its datapath and control to support a new instruction lui (load upper immediate) MI Shift eft 1 Branch Instruction 16-0 ALUSrc Instruction (19-15Read PCaddress Read register 1 Read instruction 124-20Read data 1 Zero register 2 Write Read register data 2 Write data Registers 31-01 Instruction AL Addressdata M Write Data mm84 Gen Instruction (31-0 32 ALU Instruction [30,14-121 (1). (12%) Add/modify components in the above datapath to support the execution of lui. Recall that lui shifts its 20-bit immediate field (imm[31:12] to the left by 12 bits to generate the result to be stored in the destination register rd, i.e., R[rd32b'imm, imm[31:12], 12'b0;. You can draw on the above figure directly (2), (800) The control unit of the single-cycle processor consists of a main decoder and an ALU decoder. Add an entry to the main decoder truth table to support lui Instruction opcode RegWrite ALUSrc Branch MemWrite MemRead MemtoR AL ull 0110111