Question

***I am getting an error in my code where its bold writing. I just need to build the first MUX because it needs the same

***I am getting an error in my code where its bold writing. I just need to build the first MUX because it needs the same iteration 4 times. I made a Test Bench for my Mux and it works proper, but now I dont know how to fix my error or if I am doing it correct. (This code had to be done in VHDL "VHSIC Hardware Description Language") ***

---------------------------------------------------------------------------------- library IEEE; use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating -- any Xilinx leaf cells in this code. --library UNISIM; --use UNISIM.VComponents.all;

entity DIV_CONST is Port ( dividend : in STD_LOGIC_VECTOR (7 downto 0); remainder : out STD_LOGIC_VECTOR (5 downto 0); quotient : out STD_LOGIC_VECTOR (2 downto 0)); end DIV_CONST;

architecture Behavioral of DIV_CONST is component Mux2x1 is port ( T : in STD_LOGIC_VECTOR(7 downto 0); F : in STD_LOGIC_VECTOR(7 downto 0); s : in STD_LOGIC; pout : STD_LOGIC_VECTOR(7 downto 0)); end component Mux2x1; constant fifty_three : std_logic_vector(7 downto 0) := "110101"; signal t0_sig, f0_sig,p0_sig: std_logic_vector(7 downto 0); signal t1_sig, f1_sig,p1_sig: std_logic_vector(7 downto 0); signal t2_sig, f2_sig,p2_sig: std_logic_vector(7 downto 0); signal t3_sig, f3_sig,p3_sig: std_logic_vector(7 downto 0); signal s0_sig, s1_sig, s2_sig, s3_sig: std_logic; begin -- First arithmetic connected to first 2 by 1 Mux t0_sig = fifty_three) then (s0_sig ="1") else (s0_sig = '0'); end if; u00: Mux2x1 port map(T=> t0_sig, F=> f0_sig, s=> s0_sig, pout => p0_sig); -- u01: Mux2x1 port map(); -- u02: Mux2x1 port map(); -- u03: Mux2x1 port map();

end Behavioral;

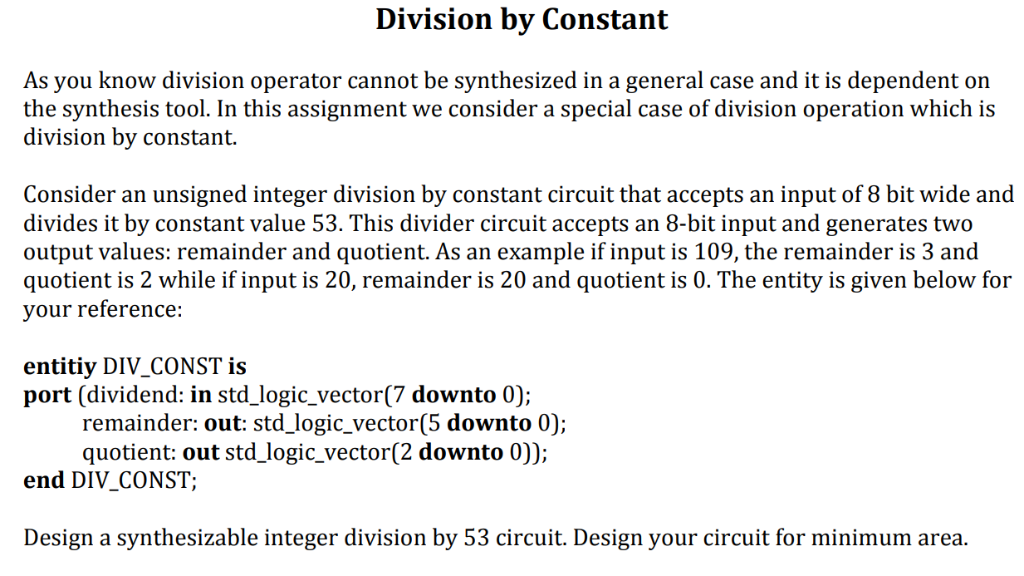

Division by Constant As you know division operator cannot be synthesized in a general case and it is dependent on the synthesis tool. In this assignment we consider a special case of division operation which is division by constant. Consider an unsigned integer division by constant circuit that accepts an input of 8 bit wide and divides it by constant value 53. This divider circuit accepts an 8-bit input and generates two output values: remainder and quotient. As an example if input is 109, the remainder is 3 and quotient is 2 while if input is 20, remainder is 20 and quotient is 0. The entity is given below for your reference: entitiy DIVCONST is port (dividend: in std_logic_vector(7 downto 0); remainder: out: std_logic_vector(5 downto 0); quotient: out std_logic_vector(2 downto 0)): end DIV_CONST; Design a synthesizable integer division by 53 circuit. Design your circuit for minimum area. Division by Constant As you know division operator cannot be synthesized in a general case and it is dependent on the synthesis tool. In this assignment we consider a special case of division operation which is division by constant. Consider an unsigned integer division by constant circuit that accepts an input of 8 bit wide and divides it by constant value 53. This divider circuit accepts an 8-bit input and generates two output values: remainder and quotient. As an example if input is 109, the remainder is 3 and quotient is 2 while if input is 20, remainder is 20 and quotient is 0. The entity is given below for your reference: entitiy DIVCONST is port (dividend: in std_logic_vector(7 downto 0); remainder: out: std_logic_vector(5 downto 0); quotient: out std_logic_vector(2 downto 0)): end DIV_CONST; Design a synthesizable integer division by 53 circuit. Design your circuit for minimum areaStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started