Question

I have started my design but am stuck and need some help with implementation. Help is appreciated! I have listed all that is needed for

I have started my design but am stuck and need some help with implementation. Help is appreciated! I have listed all that is needed for the problem.

Design a single bus gate level implementation of a machine that implements the following instruction set, using a hardwired control unit. DO NOT USE PIPELINING FOR OPTIMIZATIONS.

Characteristics:

a word size of 16-bits memory address/data bus size of 16-bits

byte addressable memory 64K byte main memory

a 16-bit program status word (PSW) with status bits. The first two bits are the condition code bits Z and N; these bits are conditionally controlled and denote the results of comparisons of the instruction result to the values zero (Z=1-equality to zero; N=1- less than zero). In addition, a third bit denotes execution in either of privileged or user mode (some operations are prohibited in user mode). The remaining bits control operations/constraints in the memory space that are not addressed in this project.

16 instructions, 2 of which can be executed only in privileged mode. Attempt to execute these 2 instructions in user mode will cause a program check violation.

8 16-bit General Purpose Registers (Reg). Register 0 (Reg[0]) always holds the value 0 no matter what value is assigned to it.

a 16-bit program counter (PC) which is also Reg[7]

a 16-bit count-down timer that causes a timer interrupt when it reaches zero provided the machine is executing in user mode. Timer interrupts are ignored when executing in privileged mode.

2s complement number representation

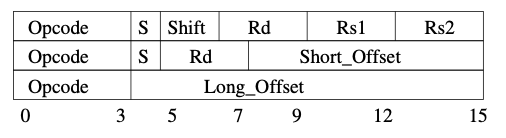

Instruction Set: Consists of 16 instructions shown in the table below.

Rd/Rs1/Rs2 specify one of the general purpose registers, S controls the setting of the condition codes (described below), and the use of the offset fields is defined in the instruction set definition. The Shift bits in the instruction cause the register value at Rs2 to be left shifted by the corresponding value (0, 1, 2, or 3).

The notation GPR[]/MM[] denotes respectively the register contents/memory contents. The condition codes are conditionally set by the result from the first and second instruction formats. The instruction bit IR.S determines if the execution of the instruction should set the condition code (1 Yes, 0 No). If set, the condition code bit (N and Z) should be set based on the value resulting from the operation. When in user mode (i.e., the PSW privileged bit (P) is not set), only the first 14 instructions can be executed. All 16 instructions can be executed in privileged mode. Attempting to execute a privileged instruction when in user mode signals a program check violation.

Exceptions:

When in user mode (i.e., the PSW privileged bit (P) is not set), only the first 14 instructions can be executed. All 16 instructions can be executed in privileged mode. Attempting to execute a privileged opcode when in user mode signals a program check violation. A program check vio- lation causes the machine to swap the PC, and PSW as follows:

1. MM[0] = PSW 2. MM[2] = PC 3. PSW = MM[4] 4. PC = MM[6]

Timeout:

There exists a count-down timer in the system that interrupts execution of instructions when executing in user mode. When this counter reaches zero, it triggers an internal state bit. This internal state bit is reset when a new value is loaded into the clock (by the CLK instruction). A timeout exception interrupt occurs when the internal state bit is set and the control unit is at an instruction boundary (between instructions). The effects of the interrupt are to modify the main memory, PC, and PSW in the following way:

1. MM[8] = PSW 2. MM[10] = PC 3. PSW = MM[12] 4. PC = MM[14]

When executing in privileged mode, the count- down timer has no effect.

Restrictions:

You may use any number of internal registers to hold intermediate values. You must restrict yourself to the single bus paradigm no point-to-point connections are allowed.

You may use a constant ROM in this design provided it contains 8 or fewer constants.

Assume that all memory operations are asynchronous.

You must develop gate level descriptions of all components except: multiplexers, demultiplexers, encoders, decoders, and flip-flops.

Ignore the details regarding the implementation of the countdown timer and define only its interface.

The currently assigned opcode values are only for illustration purposes and you may modify them in order to obtain optimization points.

*Document Optimizations, describe the trade offs of each optimization and justify them.

I have started my design but am stuck and need some help with implementation. Help is appreciated!

Rs2 Opcode Opcode Opcode 0 S Shift Rd Rs1 S Rd Short_Offset Long_Offset 5 7 9 12 3 5 15 Rs2 Opcode Opcode Opcode 0 S Shift Rd Rs1 S Rd Short_Offset Long_Offset 5 7 9 12 3 5 15Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started