Question: i need as fast as possible QUESTION 2 (40 POINTS) Write the Verilog HDL code for an 8-bit Universal Shift Register (negative-edge triggered) at the

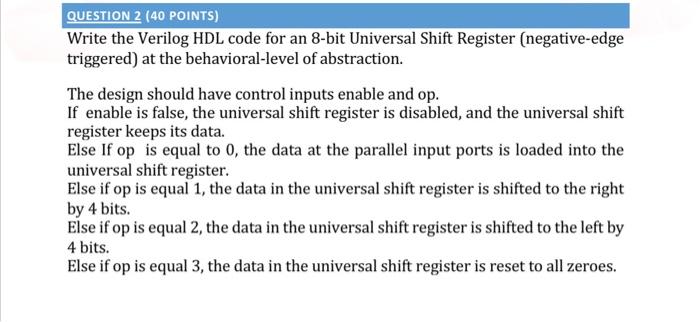

QUESTION 2 (40 POINTS) Write the Verilog HDL code for an 8-bit Universal Shift Register (negative-edge triggered) at the behavioral-level of abstraction. The design should have control inputs enable and op. If enable is false, the universal shift register is disabled, and the universal shift register keeps its data. Else If op is equal to 0, the data at the parallel input ports is loaded into the universal shift register. Else if op is equal 1, the data in the universal shift register is shifted to the right by 4 bits. Else if op is equal 2, the data in the universal shift register is shifted to the left by 4 bits. Else if op is equal 3, the data in the universal shift register is reset to all zeroes

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts