I need help with questions 4-6. Please answer all parts of each question! Thank You!

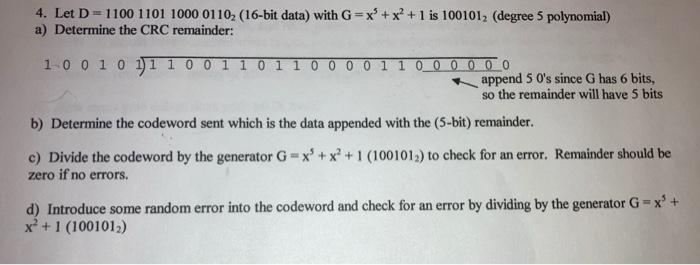

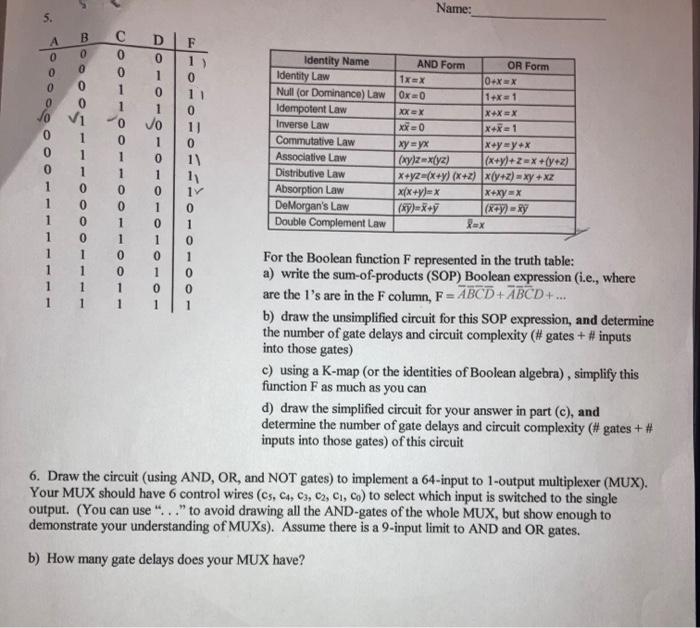

4. Let D-1100 1101 1000 01102 (16-bit data) with G = x + x + 1 is 100101, (degree 5 polynomial) a) Determine the CRC remainder: 1001 0 1 1 1 0 0 1 1 0 1 1 0 0 0 0 1 1 0 0 0 0 0 0 append 50's since G has 6 bits, so the remainder will have 5 bits b) Determine the codeword sent which is the data appended with the (5-bit) remainder. c) Divide the codeword by the generator G = x + x + 1 (1001013) to check for an error. Remainder should be zero if no errors. d) Introduce some random error into the codeword and check for an error by dividing by the generator G = x' + x +1 (1001012) Name: D F A 0 0 B 0 0 0 0 0 0 1 0 1 0 0 0 1 1 0 1 1 1 0 0 0 0 0 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1 0 1 0 1 vo 1 0 1 0 1 0 1 0 1 0 1 0 11 0 1) 0 1) 11 Identity Name Identity Law Null (or Dominance) Law Idempotent Law Inverse Law Commutative Law Associative Law Distributive Law Absorption Law De Morgan's Law Double Complement Law AND Form OR Form 1x=X 0XX Ox0 1+x=1 XXX X+X=X XX=0 x+8 = 1 xy = yx x+y = y + x wyzexlyz) (x+y)+2x+y+z) x+yz=(XY)(x+2) X(y^2) = xy + x2 x(x+y)=x X+xy X (XY)=x+y (X+Y) -- XY Pex 0 1 0 1 0 0 1 For the Boolean function F represented in the truth table: a) write the sum-of-products (SOP) Boolean expression (i.e., where are the l's are in the F column, F = ABCD +ABCD +... b) draw the unsimplified circuit for this SOP expression, and determine the number of gate delays and circuit complexity (# gates + # inputs into those gates) c) using a K-map (or the identities of Boolean algebra), simplify this function F as much as you can d) draw the simplified circuit for your answer in part (c), and determine the number of gate delays and circuit complexity (# gates + # inputs into those gates) of this circuit 6. Draw the circuit (using AND, OR, and NOT gates) to implement a 64-input to 1-output multiplexer (MUX). Your MUX should have 6 control wires (es, C4, C3, C2, C1, Co) to select which input is switched to the single output. (You can use"..." to avoid drawing all the AND-gates of the whole MUX, but show enough to demonstrate your understanding of MUXs). Assume there is a 9-input limit to AND and OR gates. b) How many gate delays does your MUX have