Answered step by step

Verified Expert Solution

Question

1 Approved Answer

I need help writing a VHDL code to convert 5211 to BCD as shown in the truth table above using only one loop statement. I

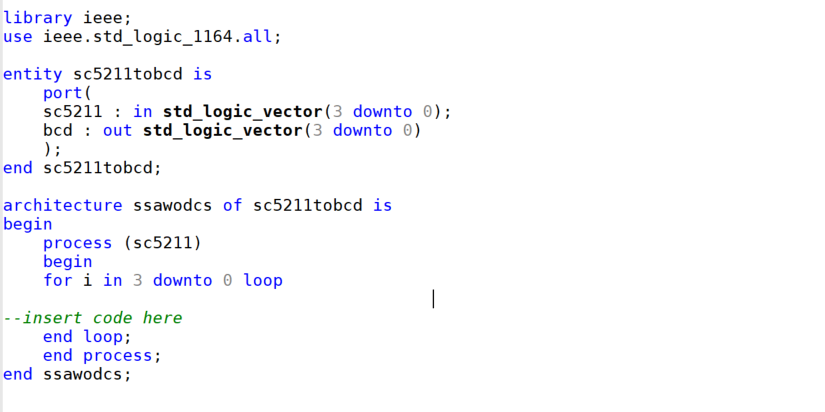

I need help writing a VHDL code to convert 5211 to BCD as shown in the truth table above using only one loop statement. I included most of the code above but I'm stuck on how the loop statement should work.

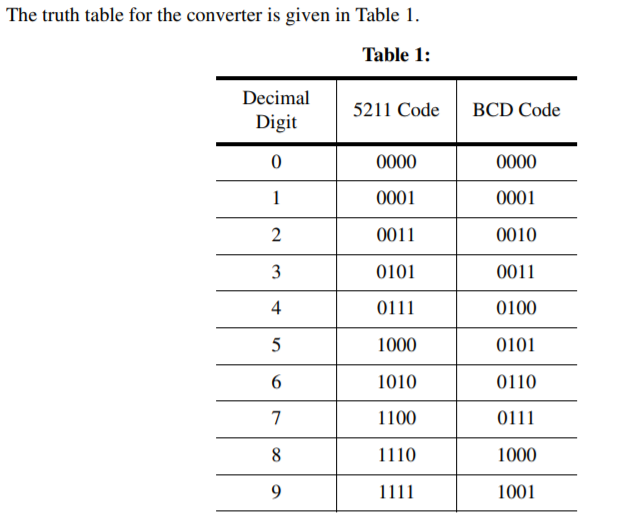

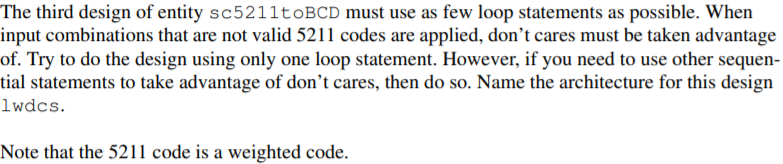

The truth table for the converter is given in Table 1. Table 1: Decimal Digit 5211 Code BCD Code 0 0000 0000 1 0001 0001 2 0011 0010 3 0101 0011 4 0111 0100 5 1000 0101 6 1010 0110 7 1100 0111 8 1110 1000 9 1111 1001 The third design of entity sc521100BCD must use as few loop statements as possible. When input combinations that are not valid 5211 codes are applied, don't cares must be taken advantage of. Try to do the design using only one loop statement. However, if you need to use other sequen- tial statements to take advantage of don't cares, then do so. Name the architecture for this design lwdcs. Note that the 5211 code is a weighted code. library ieee; use ieee.std_logic_1164.all; entity sc5211tobcd is porta sc5211 : in std_logic_vector(3 downto 0); bcd : out std_logic_vector(3 downto 0) ); end sc5211tobcd; architecture ssawodcs of sc5211tobcd is begin process (sc5211) begin for i in 3 downto o loop --insert code here end loop; end process; end ssawodcs; The truth table for the converter is given in Table 1. Table 1: Decimal Digit 5211 Code BCD Code 0 0000 0000 1 0001 0001 2 0011 0010 3 0101 0011 4 0111 0100 5 1000 0101 6 1010 0110 7 1100 0111 8 1110 1000 9 1111 1001 The third design of entity sc521100BCD must use as few loop statements as possible. When input combinations that are not valid 5211 codes are applied, don't cares must be taken advantage of. Try to do the design using only one loop statement. However, if you need to use other sequen- tial statements to take advantage of don't cares, then do so. Name the architecture for this design lwdcs. Note that the 5211 code is a weighted code. library ieee; use ieee.std_logic_1164.all; entity sc5211tobcd is porta sc5211 : in std_logic_vector(3 downto 0); bcd : out std_logic_vector(3 downto 0) ); end sc5211tobcd; architecture ssawodcs of sc5211tobcd is begin process (sc5211) begin for i in 3 downto o loop --insert code here end loop; end process; end ssawodcsStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started