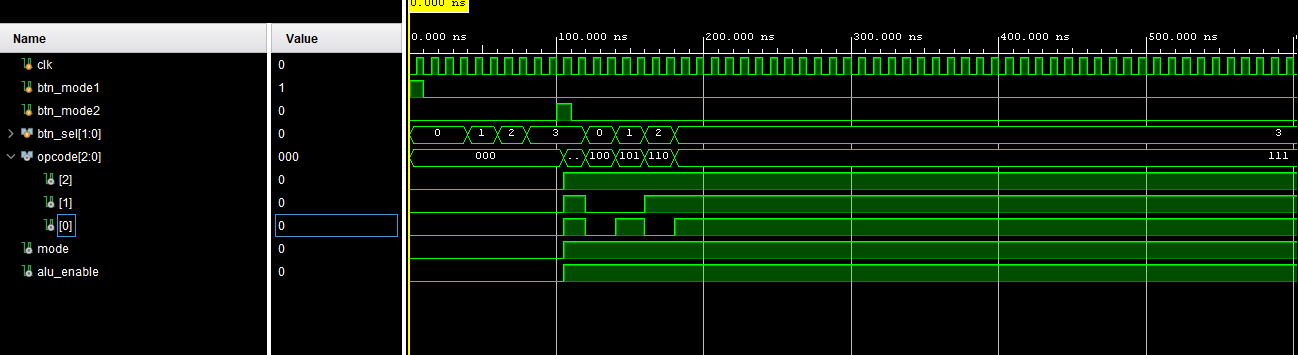

Question: I need these fix the first mode isn't showing on the opcode and i need a ALC for the opcode and enable to go to

I need these fix the first mode isn't showing on the opcode and i need a ALC for the opcode and enable to go to four segment and led display. the input are a: and b: module calculatorfsm

input clk Clock signal

input btnmode Button for Mode Arithmetic

input btnmode Button for Mode Bitwise

input : btnsel, Button to select operation

output reg : opcode, bit opcode for ALU

output reg mode, bit mode Arithmetic, Bitwise

output reg aluenable Enable signal for ALU

;

State Encoding

localparam MODEb; Mode : Arithmetic operations

localparam MODEb; Mode : Bitwise operations

State register to store current mode

reg currentmode;

reg btnmodelast, btnmodelast; To detect button press edge for mode toggle

FSM State Transition

always @posedge clk begin

Detect button press to toggle between modes

if btnmode && btnmodelast begin

currentmode MODE; Select Mode Arithmetic

end else if btnmode && btnmodelast begin

currentmode MODE; Select Mode Bitwise

end

btnmodelast btnmode; Update button state for mode

btnmodelast btnmode; Update button state for mode

end

Output and operation selection based on current mode and btnsel

always @ begin

Default values

aluenable ; Initially disable ALU

case currentmode

MODE: begin

mode ; Arithmetic Mode

case btnsel

b: begin

opcode b; Addition

aluenable ; Enable ALU

end

b: begin

opcode b; Subtraction

aluenable ; Enable ALU

end

b: begin

opcode b; Multiplication

aluenable ; Enable ALU

end

b: begin

opcode b; Division

aluenable ; Enable ALU

end

default: begin

opcode b; Default to Addition

aluenable ; Enable ALU

end

endcase

end

MODE: begin

mode ; Bitwise Mode

case btnsel

b: begin

opcode b; AND

aluenable ; Enable ALU

end

b: begin

opcode b; OR

aluenable ; Enable ALU

end

b: begin

opcode b; Shift Left

aluenable ; Enable ALU

end

b: begin

opcode b; Shift Right

aluenable ; Enable ALU

end

default: begin

opcode b; Default to AND

aluenable ; Enable ALU

end

endcase

end

default: begin

mode ;

opcode b;

aluenable ;

end

endcase

end

endmodule

module calculatorfsmtb;

Declare testbench signals

reg clk; Clock signal

reg btnmode btnmode; Buttons for mode selection

reg : btnsel; Button to select operation

wire : opcode; ALU opcode output

wire mode; Mode output Arithmetic, Bitwise

wire aluenable; ALU enable output

Instantiate the calculator FSM

calculatorfsm uut

clkclk

btnmodebtnmode

btnmodebtnmode

btnselbtnsel

opcodeopcode

modemode

aluenablealuenable

;

Clock generation

always begin

# clk ~clk; Generate a clock with a period of time units

end

Testbench stimulus to check opcode for both modes

initial begin

Initialize inputs

clk ;

btnmode;

btnmode;

btnsel b; Test Addition opcode should be b

Test Mode Arithmetic

btnmode; Select Arithmetic mode

#;

btnmode;

#;

Test different arithmetic operations

btnsel b; Addition opcode should be b

#;

btnsel b; Subtraction opcode should be b

#;

btnsel b; Multiplication opcode should be b

#;

btnsel b; Division opcode should be b

#;

Test Mode Bitwise

btnmode; Select Bitwise mode

#;

btnmode;

#;

Test bitwise operations

btnsel b; AND opcode should be b

#;

btnsel b; OR opcode should be b

#;

btnsel b; Shift Left opcode should be b

#;

btnsel b; Shift Right opcode should be b

#;

end

endmodule

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock