Answered step by step

Verified Expert Solution

Question

1 Approved Answer

I would like to know how to solve this. I will need a detailed explanation, please. Thank you! 4. The following table shows the breakdown

I would like to know how to solve this. I will need a detailed explanation, please. Thank you!

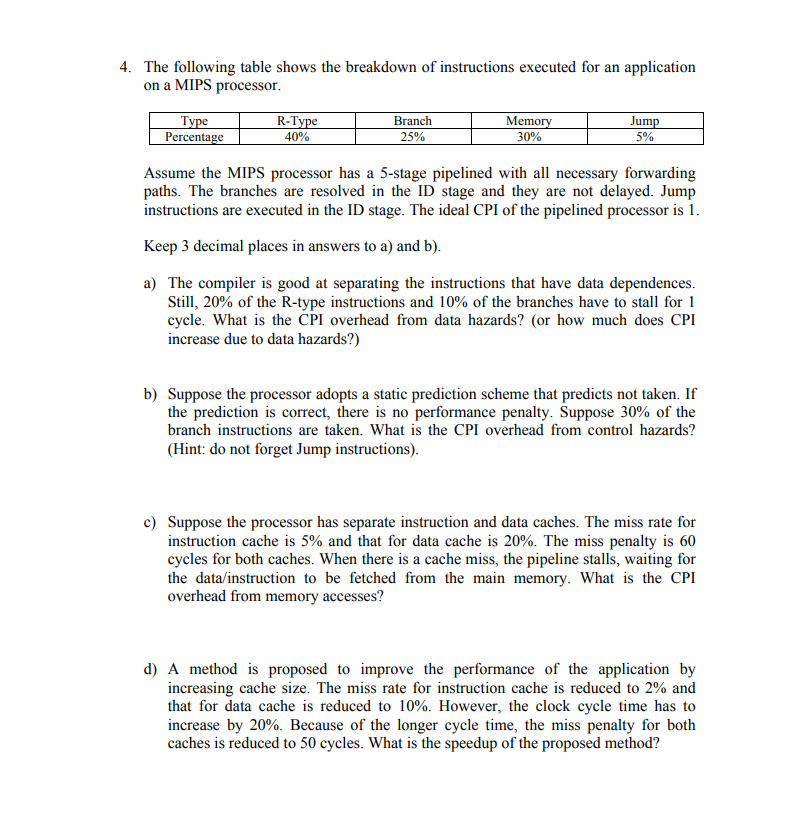

4. The following table shows the breakdown of instructions executed for an application on a MIPS processor R-T Branch Me Jum Percentage 40% 25% 30% 5% Assume the MIPS processor has a 5-stage pipelined with all necessary forwarding paths. The branches are resolved in the ID stage and they are not delayed. Jump instructions are executed in the ID stage. The ideal CPI of the pipelined processor is 1 Keep 3 decimal places in answers to a) and b) a) The compiler is good at separating the instructions that have data dependences. Still, 20% of the R-type instructions and 10% of the branches have to stall for l cycle. What is the CPI overhead from data hazards? (or how much does CPI increase due to data hazards?) b) Suppose the processor adopts a static prediction scheme that predicts not taken. If the prediction is correct, there is no performance penalty. Suppose 30% of the branch instructions are taken. What is the CPI overhead from control hazards? (Hint: do not forget Jump instructions) c) Suppose the processor has separate instruction and data caches. The miss rate for instruction cache is 5% and that for data cache is 20%. The miss penalty is 60 cycles for both caches. When there is a cache miss, the pipeline stalls, waiting for the data/instruction to be fetched from the main memory. What is the CPI overhead from memory accesses? d) A method is proposed to improve the performance of the application by increasing cache size. The miss rate for instruction cache is reduced to 2% and that for data cache is reduced to 10%. However, the clock cycle time has to increase by 20%. Because of the longer cycle time, the miss penalty for both caches is reduced to 50 cycles. What is the speedup of the proposed method? 4. The following table shows the breakdown of instructions executed for an application on a MIPS processor R-T Branch Me Jum Percentage 40% 25% 30% 5% Assume the MIPS processor has a 5-stage pipelined with all necessary forwarding paths. The branches are resolved in the ID stage and they are not delayed. Jump instructions are executed in the ID stage. The ideal CPI of the pipelined processor is 1 Keep 3 decimal places in answers to a) and b) a) The compiler is good at separating the instructions that have data dependences. Still, 20% of the R-type instructions and 10% of the branches have to stall for l cycle. What is the CPI overhead from data hazards? (or how much does CPI increase due to data hazards?) b) Suppose the processor adopts a static prediction scheme that predicts not taken. If the prediction is correct, there is no performance penalty. Suppose 30% of the branch instructions are taken. What is the CPI overhead from control hazards? (Hint: do not forget Jump instructions) c) Suppose the processor has separate instruction and data caches. The miss rate for instruction cache is 5% and that for data cache is 20%. The miss penalty is 60 cycles for both caches. When there is a cache miss, the pipeline stalls, waiting for the data/instruction to be fetched from the main memory. What is the CPI overhead from memory accesses? d) A method is proposed to improve the performance of the application by increasing cache size. The miss rate for instruction cache is reduced to 2% and that for data cache is reduced to 10%. However, the clock cycle time has to increase by 20%. Because of the longer cycle time, the miss penalty for both caches is reduced to 50 cycles. What is the speedup of the proposed methodStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started