If you don't know VDHL solve first parts at least

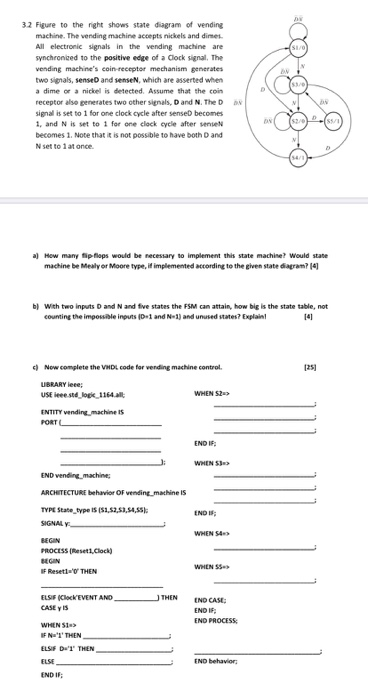

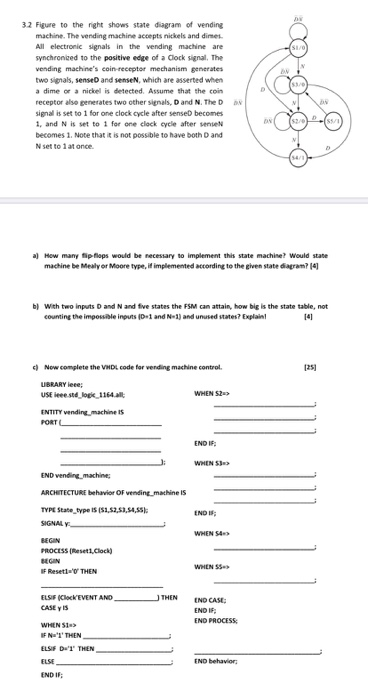

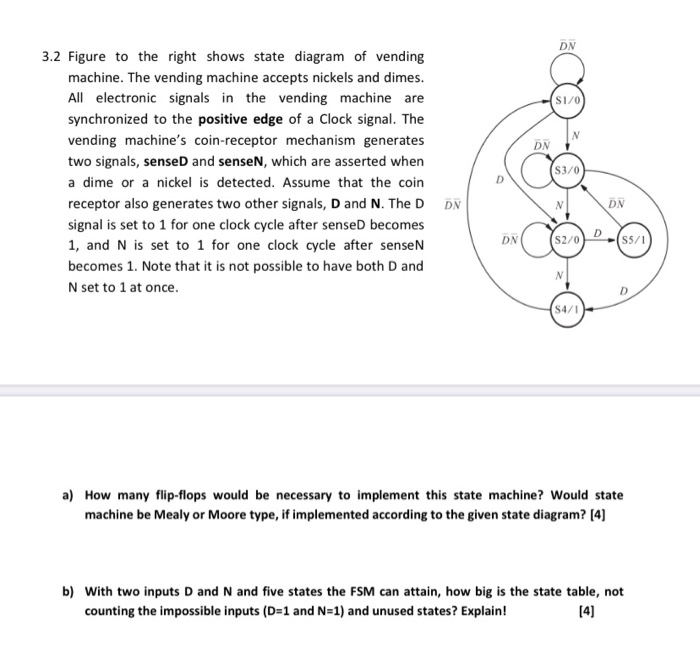

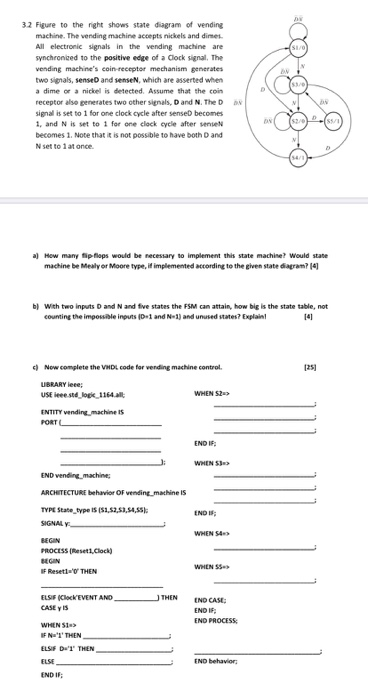

32 Figure to the right shows state diagram of vending machine. The vending machine accepts nickels and dimes. All electronic signals in the vending machine are synchronged to the positive edge of a Clock signal. The vending machine's coin receptor mechanism generates two signals, sense and sense, which are asserted when a dime or a nickel is detected. Assume that the coin receptor also generates two other signals, D and N. The D signal is set to 1 for one clock cycle after sense becomes 1, and N is set to 1 for one clock cycle after sensen becomes 1. Note that it is not possible to have both D and N set to 1 at once DM a) How many flip flops would be necessary to implement this state machine? Would state machine be Mealy or Moore type, if implemented according to the given state diagram? (4 b) with two inputs and N and five states the FSM can attain, how big is the state table, not counting the impossible inputs 1 and N-1) and unused states? Explain 14 Now complete the VHDL code for vending machine control UBRARYleee; USE ieee sed lock 1164 allt WHEN S2-> ENTITY vending machine is PORT 21 END IF WHEN SIE END vending machine ARCHITECTURE behavior of vending machine IS TYPE State type S (51,52,51,54,55 SIGNAL END IF WHEN 54-> BEGIN PROCESS Reset Clock) BEGIN IF Reset' THEN WHENS ELSIF (Clock'EVENT AND CASE IS THEN END CASE: END IF END PROCESS WHENSI FN'T' THEN ELSIF D-'1' THEN ELSE END IF END behavior: 3.2 Figure to the right shows state diagram of vending machine. The vending machine accepts nickels and dimes. All electronic signals in the vending machine are synchronized to the positive edge of a Clock signal. The vending machine's coin-receptor mechanism generates two signals, sense and senseN, which are asserted when a dime or a nickel is detected. Assume that the coin receptor also generates two other signals, D and N. The D signal is set to 1 for one clock cycle after sense becomes 1, and N is set to 1 for one clock cycle after sensen becomes 1. Note that it is not possible to have both D and N set to 1 at once. DN a) How many flip-flops would be necessary to implement this state machine? Would state machine be Mealy or Moore type, if implemented according to the given state diagram? [4) b) With two inputs D and N and five states the FSM can attain, how big is the state table, not counting the impossible inputs (D=1 and N=1) and unused states? Explain! (4) 32 Figure to the right shows state diagram of vending machine. The vending machine accepts nickels and dimes. All electronic signals in the vending machine are synchronged to the positive edge of a Clock signal. The vending machine's coin receptor mechanism generates two signals, sense and sense, which are asserted when a dime or a nickel is detected. Assume that the coin receptor also generates two other signals, D and N. The D signal is set to 1 for one clock cycle after sense becomes 1, and N is set to 1 for one clock cycle after sensen becomes 1. Note that it is not possible to have both D and N set to 1 at once DM a) How many flip flops would be necessary to implement this state machine? Would state machine be Mealy or Moore type, if implemented according to the given state diagram? (4 b) with two inputs and N and five states the FSM can attain, how big is the state table, not counting the impossible inputs 1 and N-1) and unused states? Explain 14 Now complete the VHDL code for vending machine control UBRARYleee; USE ieee sed lock 1164 allt WHEN S2-> ENTITY vending machine is PORT 21 END IF WHEN SIE END vending machine ARCHITECTURE behavior of vending machine IS TYPE State type S (51,52,51,54,55 SIGNAL END IF WHEN 54-> BEGIN PROCESS Reset Clock) BEGIN IF Reset' THEN WHENS ELSIF (Clock'EVENT AND CASE IS THEN END CASE: END IF END PROCESS WHENSI FN'T' THEN ELSIF D-'1' THEN ELSE END IF END behavior: 3.2 Figure to the right shows state diagram of vending machine. The vending machine accepts nickels and dimes. All electronic signals in the vending machine are synchronized to the positive edge of a Clock signal. The vending machine's coin-receptor mechanism generates two signals, sense and senseN, which are asserted when a dime or a nickel is detected. Assume that the coin receptor also generates two other signals, D and N. The D signal is set to 1 for one clock cycle after sense becomes 1, and N is set to 1 for one clock cycle after sensen becomes 1. Note that it is not possible to have both D and N set to 1 at once. DN a) How many flip-flops would be necessary to implement this state machine? Would state machine be Mealy or Moore type, if implemented according to the given state diagram? [4) b) With two inputs D and N and five states the FSM can attain, how big is the state table, not counting the impossible inputs (D=1 and N=1) and unused states? Explain! (4)