Question

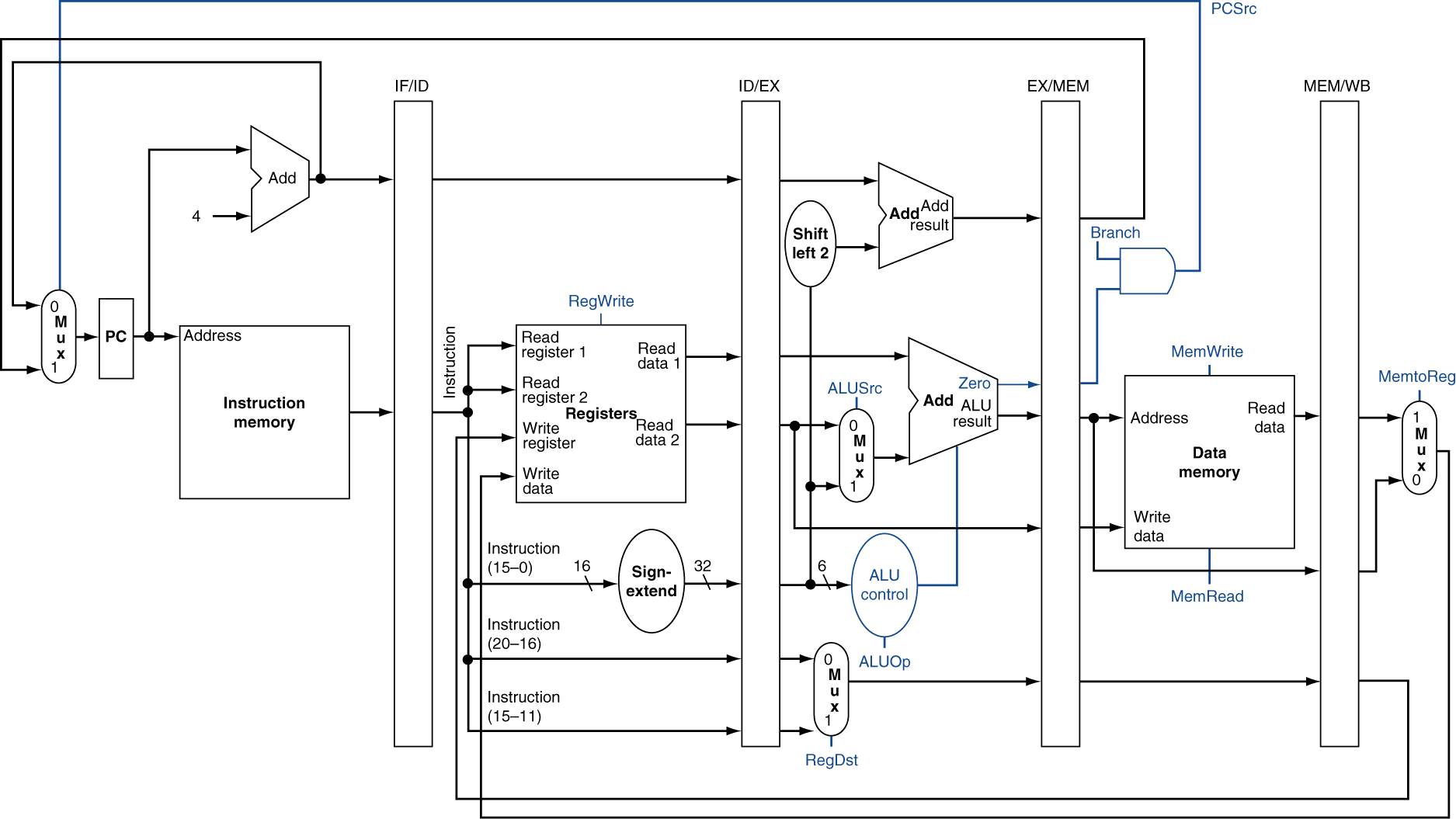

I-Mem Add Mux ALU Regs D-Mem Sign-Extend Shift-Left-2 200ps 70ps 20ps 90ps 90ps 250ps 15ps 10ps Figure 1: Pipeline datapath with control signals identified 1)If

| I-Mem | Add | Mux | ALU | Regs | D-Mem | Sign-Extend | Shift-Left-2 |

| 200ps | 70ps | 20ps | 90ps | 90ps | 250ps | 15ps | 10ps |

Figure 1: Pipeline datapath with control signals identified

1)If the only thing we need to do in a processor is fetch consecutive instructions (Figure 1), what would the cycle time be?

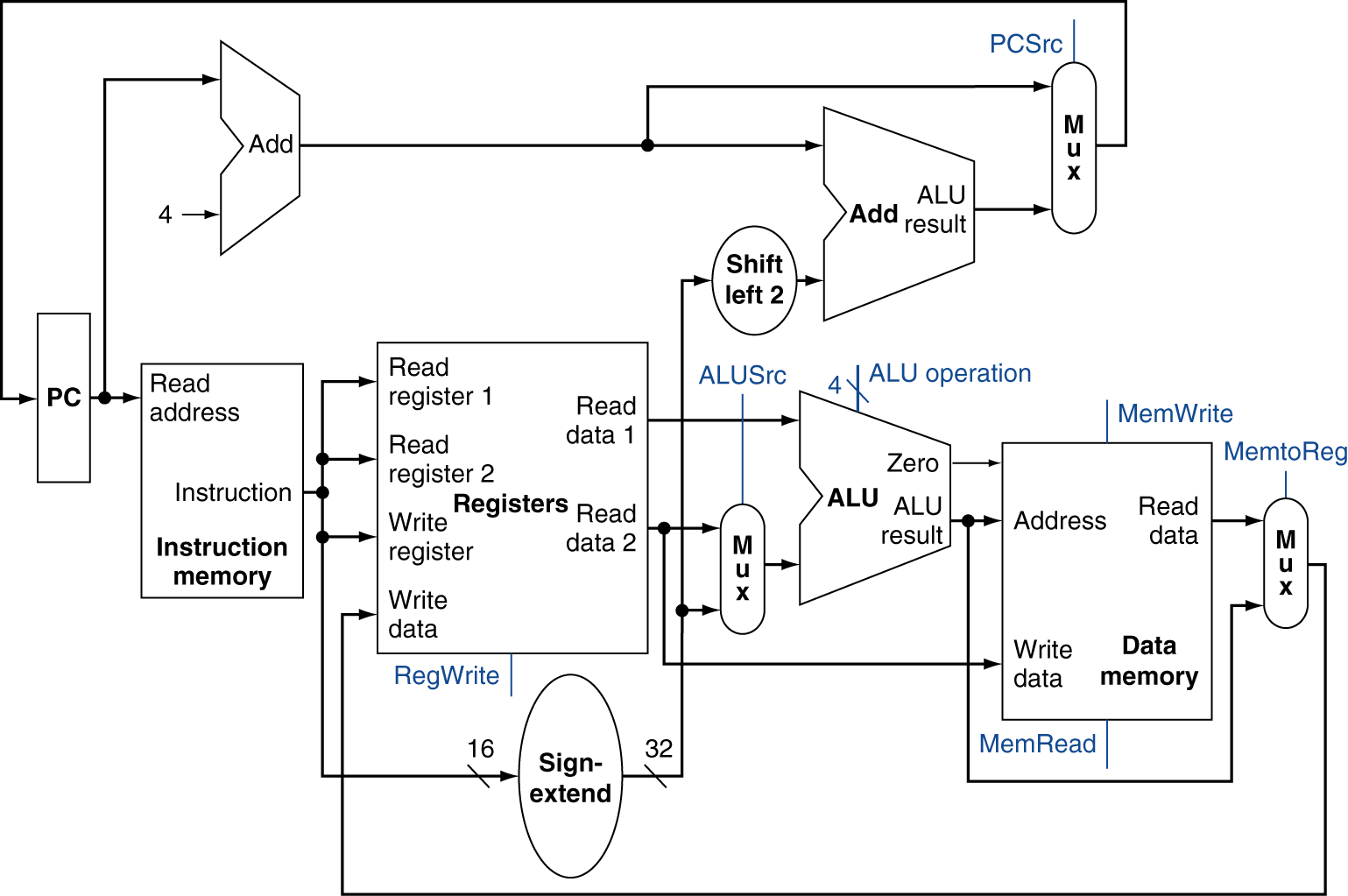

2)Consider a datapath similar to the one in Figure 2, but for a processor that only has one type of instruction: unconditional PC-relative branch. What would the cycle time be for this datapath?

3)Repeat question 2) but this time we need to support only conditional PC-relative branches.

The remaining three questions in this exercise refer to datapath element Shift-Left-2:

4)Which kinds of instructions require this resource?

5)For which kinds of instructions (if any) is this resource on the critical path?

6)Assuming that we only support beq and add instructions, discuss how changes in the given latency of this resource affect the cycle time of the processor. Assume that the latencies of other resources do not change.

Figure 2: Simple datapath

PCSrc IF/ID ID/EX EX/MEM MEM/WEB Add AddAdd result 4 Shift left 2 Branch RegWrite PC Address Read register 1 Read data 1 MemWrite MemtoReg Read register 2 Zero Add ALU result ALUSrc Instruction memor)y Read data Registers Address Write register Read data 2 Write data memory Write data Instruction (15-0) 16 Sign32 extend ALU control MemRead Instruction (20-16) 0 ALUOp Instruction (15-11) RegDstStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started