Answered step by step

Verified Expert Solution

Question

1 Approved Answer

In a system with 2-level paging, each virtual adderss (p1, p2, d) requires three memory references. To speed up the address translation, a TLB holds

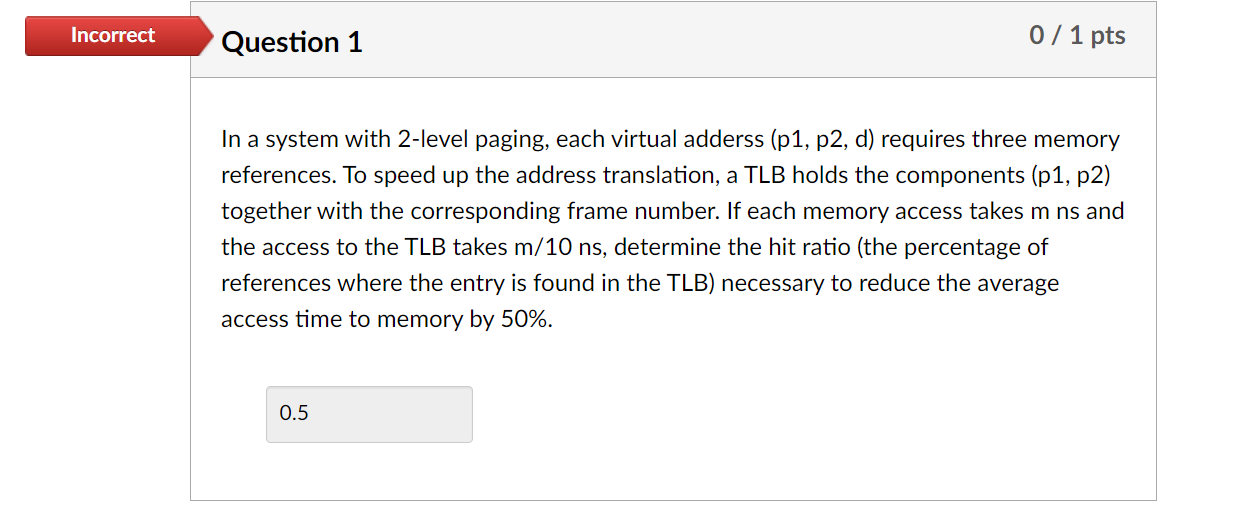

In a system with 2-level paging, each virtual adderss (p1, p2, d) requires three memory references. To speed up the address translation, a TLB holds the components (p1, p2) together with the corresponding frame number. If each memory access takes m ns and the access to the TLB takes m/10 ns, determine the hit ratio (the percentage of references where the entry is found in the TLB) necessary to reduce the average access time to memory by 50%.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started