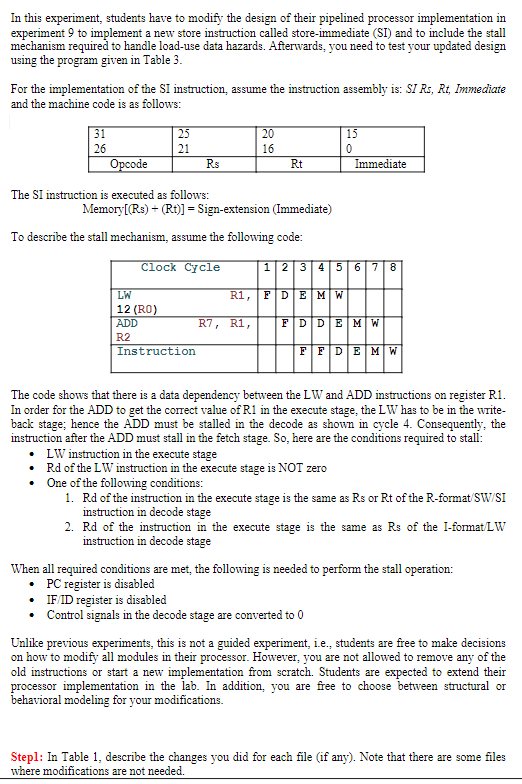

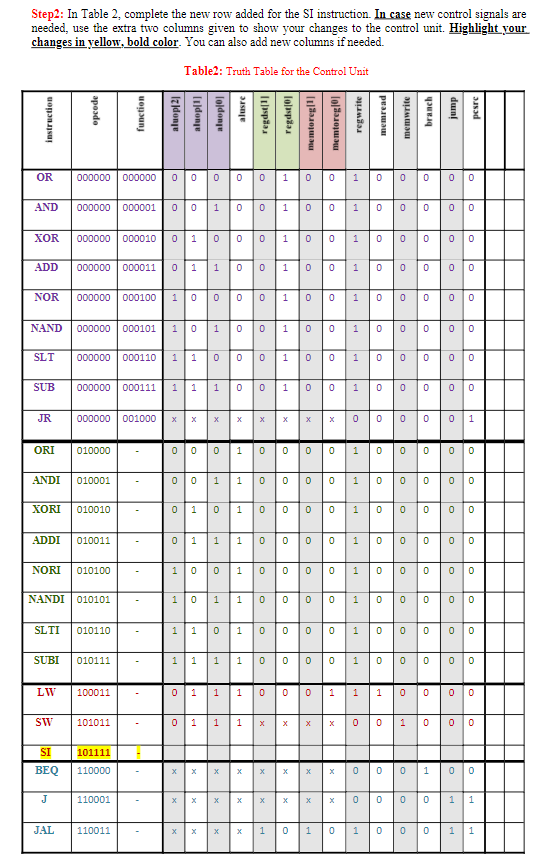

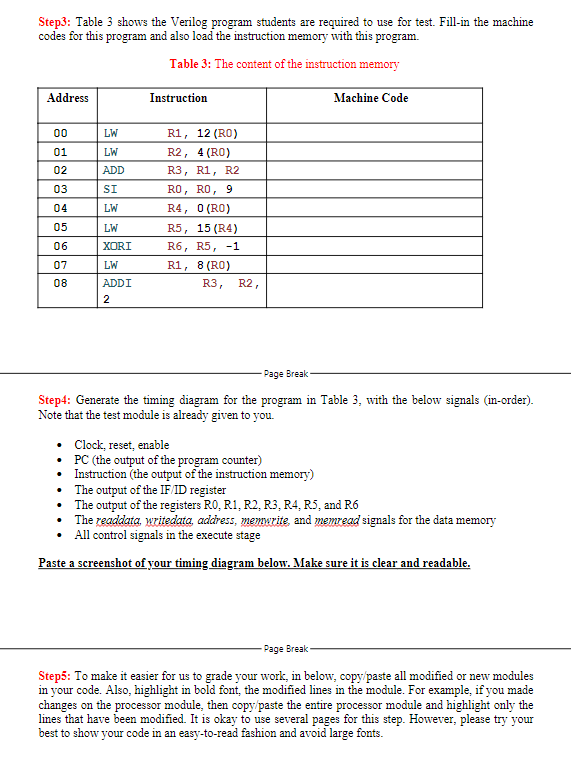

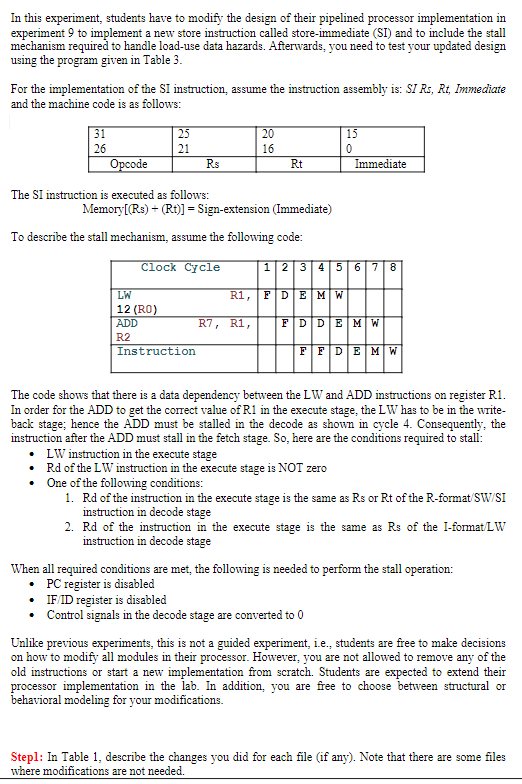

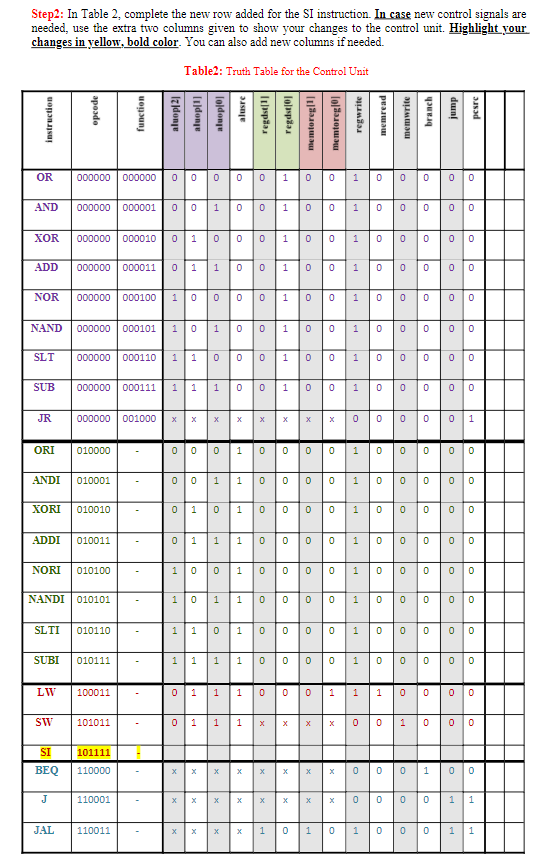

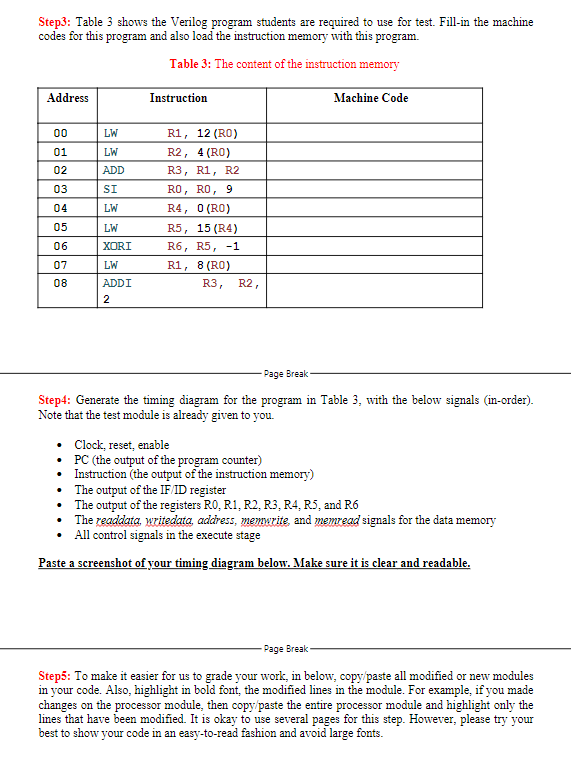

In this experiment, students have to modify the design of their pipelined processor implementation in experiment 9 to implement a new store instruction called store-immediate (SI) and to include the stall mechanism required to handle load-use data hazards. Afterwards, you need to test your updated design using the program given in Table 3 . For the implementation of the SI instruction, assume the instruction assembly is: SI Rs, Rt, Immediate and the machine code is as follows: The SI instruction is executed as follows: Memory [(Rs)+(Rt)]= Sign-extension (Immediate) To describe the stall mechanism, assume the following code: The code shows that there is a data dependency between the LW and ADD instructions on register R1. In order for the ADD to get the correct value of R1 in the execute stage, the LW has to be in the writeback stage; hence the ADD must be stalled in the decode as shown in cycle 4. Consequently, the instruction after the ADD must stall in the fetch stage. So, here are the conditions required to stall: - LW instruction in the execute stage - Rd of the LW instruction in the execute stage is NOT zero - One of the following conditions: 1. Rd of the instruction in the execute stage is the same as Rs or R. of the R-format SW/SI instruction in decode stage 2. Rd of the instruction in the execute stage is the same as Rs of the I-format/LW instruction in decode stage When all required conditions are met, the following is needed to perform the stall operation: - PC register is disabled - IF/ID register is disabled - Control signals in the decode stage are converted to 0 Unlike previous experiments, this is not a guided experiment, i.e., students are free to make decisions on how to modify all modules in their processor. However, you are not allowed to remove any of the old instructions or start a new implementation from scratch. Students are expected to extend their processor implementation in the lab. In addition, you are free to choose between structural or behavioral modeling for your modifications. Stepl: In Table 1, describe the changes you did for each file (if any). Note that there are some files where modifications are not needed. Step2: In Table 2, complete the new row added for the SI instruction. In case new control signals are needed, use the extra two columns given to show your changes to the control unit. Highlight your changes in yellow, bold color. You can also add new columns if needed. Step3: Table 3 shows the Verilog program students are required to use for test. Fill-in the machine codes for this program and also load the instruction memory with this program. Table 3: The content of the instruction memory Page Break Step4: Generate the timing diagram for the program in Table 3, with the below signals (in-order). Note that the test module is already given to you. - Clock, reset, enable - PC (the output of the program counter) - Instruction (the output of the instruction memory) - The output of the IF/ID register - The output of the registers R0, R1, R2, R3, R4, R.5, and R6 - The readdata, writedata, address, memwrite, and memread signals for the data memory - All control signals in the execute stage Paste a screenshot of your timing diagram below. Make sure it is clear and readable. Page Break Step5: To make it easier for us to grade your work, in below, copy/paste all modified or new modules in your code. Also, highlight in bold font, the modified lines in the module. For example, if you made changes on the processor module, then copy/paste the entire processor module and highlight only the lines that have been modified. It is okay to use several pages for this step. However, please try your best to show your code in an easy-to-read fashion and avoid large fonts