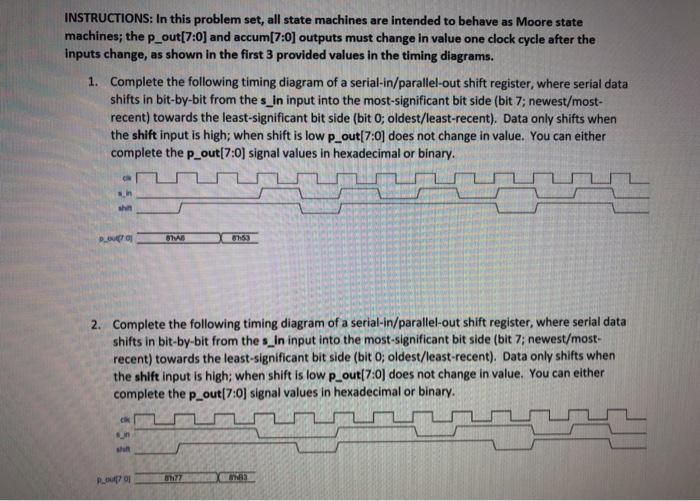

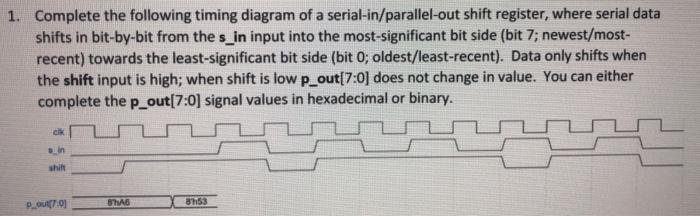

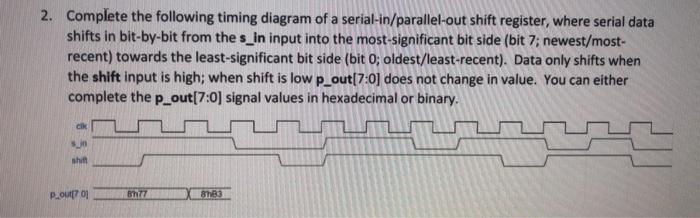

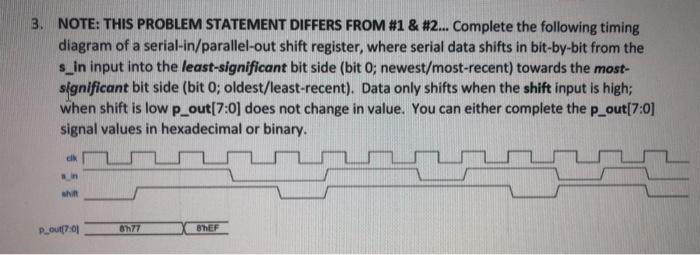

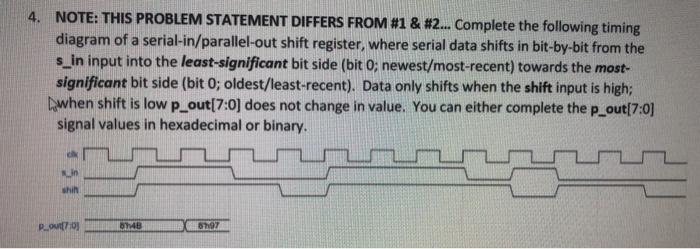

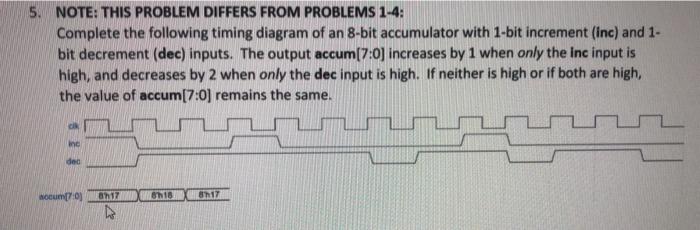

INSTRUCTIONS: In this problem set, all state machines are intended to behave as Moore state machines; the p_out(7:0) and accum[7:0) outputs must change in value one clock cycle after the inputs change, as shown in the first 3 provided values in the timing diagrams. 1. Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the most significant bit side (bit 7; newest/most- recent) towards the least-significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out(7:0) signal values in hexadecimal or binary. sh D_BUT BAB 0253 2. Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the most significant bit side (bit 7; newest/most- recent) towards the least-significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out(7:0) signal values in hexadecimal or binary. RU MAS 1. Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the most-significant bit side (bit 7; newest/most- recent) towards the least-significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out(7:0) signal values in hexadecimal or binary. Shift 0) Shab 853 2. Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the most significant bit side (bit 7; newest/most- recent) towards the least-significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out(7:0) signal values in hexadecimal or binary. cl un shi POU701 B77 8183 3. NOTE: THIS PROBLEM STATEMENT DIFFERS FROM #1 & #2... Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the least-significant bit side (bit 0; newest/most-recent) towards the most- significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out[7:0] signal values in hexadecimal or binary. IN w pour] Oh77 BEF 4. NOTE: THIS PROBLEM STATEMENT DIFFERS FROM #1 & #2... Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the least-significant bit side (bit 0; newest/most-recent) towards the most- significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out(7:0) signal values in hexadecimal or binary. Un shi Pou7i0 146 shoz 5. NOTE: THIS PROBLEM DIFFERS FROM PROBLEMS 1-4: Complete the following timing diagram of an 8-bit accumulator with 1-bit increment (inc) and 1. bit decrement (dec) inputs. The output accum(7:0) increases by 1 when only the Inc input is high, and decreases by 2 when only the dec input is high. If neither is high or if both are high, the value of accum[7:0) remains the same. ded Nom:0) Sh17 Shis Bhi INSTRUCTIONS: In this problem set, all state machines are intended to behave as Moore state machines; the p_out(7:0) and accum[7:0) outputs must change in value one clock cycle after the inputs change, as shown in the first 3 provided values in the timing diagrams. 1. Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the most significant bit side (bit 7; newest/most- recent) towards the least-significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out(7:0) signal values in hexadecimal or binary. sh D_BUT BAB 0253 2. Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the most significant bit side (bit 7; newest/most- recent) towards the least-significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out(7:0) signal values in hexadecimal or binary. RU MAS 1. Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the most-significant bit side (bit 7; newest/most- recent) towards the least-significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out(7:0) signal values in hexadecimal or binary. Shift 0) Shab 853 2. Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the most significant bit side (bit 7; newest/most- recent) towards the least-significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out(7:0) signal values in hexadecimal or binary. cl un shi POU701 B77 8183 3. NOTE: THIS PROBLEM STATEMENT DIFFERS FROM #1 & #2... Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the least-significant bit side (bit 0; newest/most-recent) towards the most- significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out[7:0] signal values in hexadecimal or binary. IN w pour] Oh77 BEF 4. NOTE: THIS PROBLEM STATEMENT DIFFERS FROM #1 & #2... Complete the following timing diagram of a serial-in/parallel-out shift register, where serial data shifts in bit-by-bit from the s_in input into the least-significant bit side (bit 0; newest/most-recent) towards the most- significant bit side (bit 0; oldest/least-recent). Data only shifts when the shift input is high; when shift is low p_out(7:0) does not change in value. You can either complete the p_out(7:0) signal values in hexadecimal or binary. Un shi Pou7i0 146 shoz 5. NOTE: THIS PROBLEM DIFFERS FROM PROBLEMS 1-4: Complete the following timing diagram of an 8-bit accumulator with 1-bit increment (inc) and 1. bit decrement (dec) inputs. The output accum(7:0) increases by 1 when only the Inc input is high, and decreases by 2 when only the dec input is high. If neither is high or if both are high, the value of accum[7:0) remains the same. ded Nom:0) Sh17 Shis Bhi