its a 3 part question the first two pictures is the same question just the other part of the diagram, the next two pictures are each separete

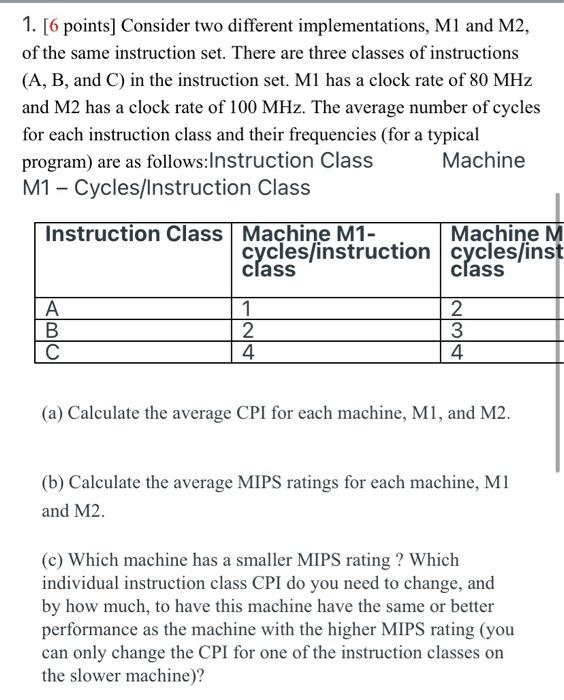

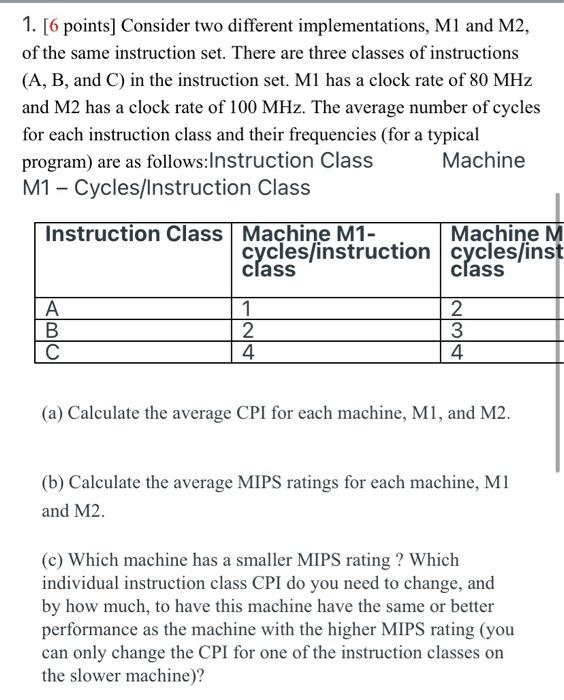

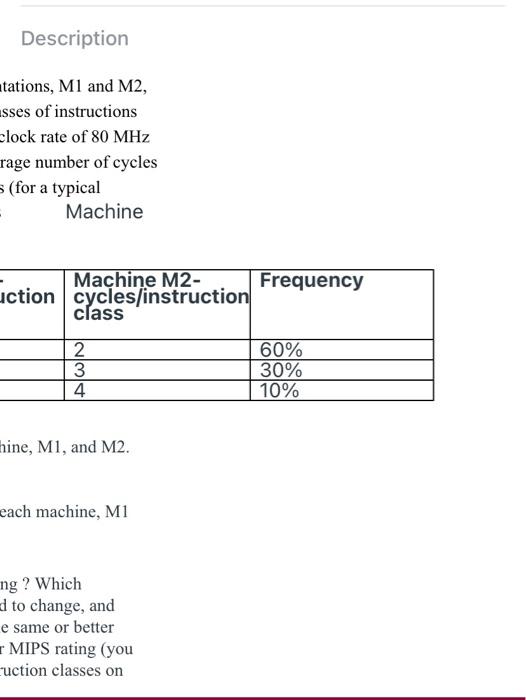

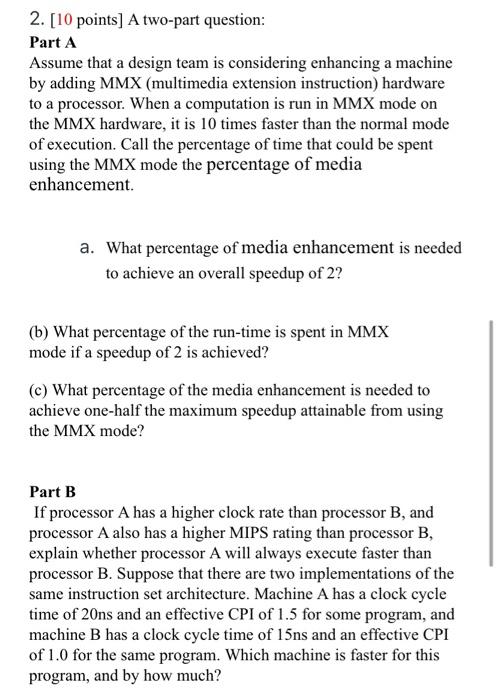

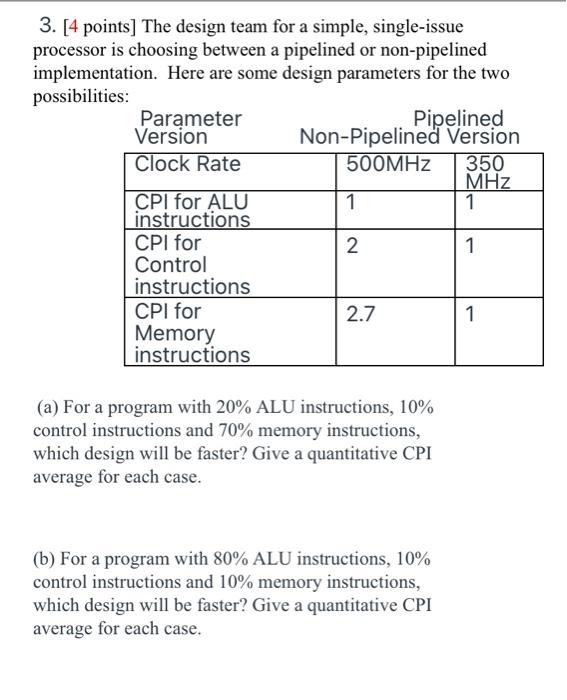

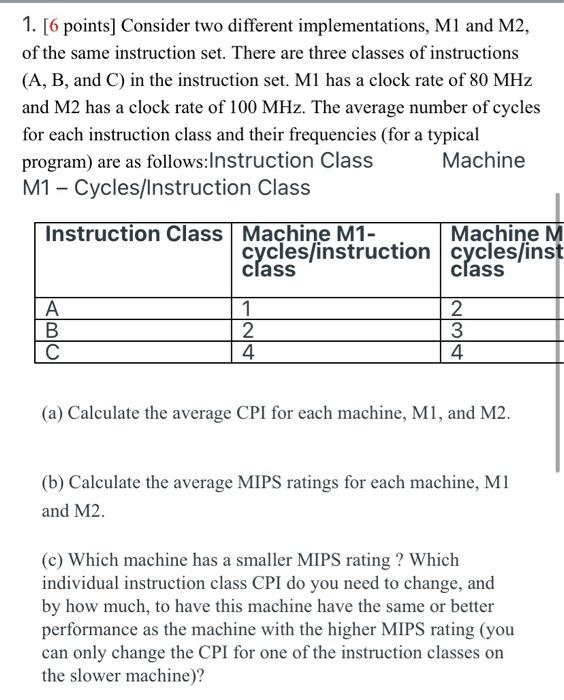

1. [6 points] Consider two different implementations, M1 and M2, of the same instruction set. There are three classes of instructions (A, B, and C) in the instruction set. M1 has a clock rate of 80 MHz and M2 has a clock rate of 100 MHz. The average number of cycles for each instruction class and their frequencies (for a typical program) are as follows:Instruction Class Machine M1 - Cycles/Instruction Class Instruction Class Machine M1- Machine M cycles/instruction cycles/inst class class A B 1 2 4 2 3 4 (a) Calculate the average CPI for each machine, MI, and M2. (b) Calculate the average MIPS ratings for each machine, Mi and M2. (c) Which machine has a smaller MIPS rating ? Which individual instruction class CPI do you need to change, and by how much, to have this machine have the same or better performance as the machine with the higher MIPS rating (you can only change the CPI for one of the instruction classes on the slower machine)? Description tations, M1 and M2, sses of instructions clock rate of 80 MHz rage number of cycles (for a typical - Machine Machine M2- Frequency action cycles/instruction class 2 3 4 60% 30% 10% hine, MI, and M2. each machine, MI ng ? Which d to change, and e same or better MIPS rating (you ruction classes on 2. [10 points] A two-part question: Part A Assume that a design team is considering enhancing a machine by adding MMX (multimedia extension instruction) hardware to a processor. When a computation is run in MMX mode on the MMX hardware, it is 10 times faster than the normal mode of execution. Call the percentage of time that could be spent using the MMX mode the percentage of media enhancement. a. What percentage of media enhancement is needed to achieve an overall speedup of 2? (b) What percentage of the run-time is spent in MMX mode if a speedup of 2 is achieved? (c) What percentage of the media enhancement is needed to achieve one-half the maximum speedup attainable from using the MMX mode? Part B If processor A has a higher clock rate than processor B, and processor A also has a higher MIPS rating than processor B, explain whether processor A will always execute faster than processor B. Suppose that there are two implementations of the same instruction set architecture. Machine A has a clock cycle time of 20ns and an effective CPI of 1.5 for some program, and machine B has a clock cycle time of 15ns and an effective CPI of 1.0 for the same program. Which machine is faster for this program, and by how much? 3. [4 points] The design team for a simple, single-issue processor is choosing between a pipelined or non-pipelined implementation. Here are some design parameters for the two possibilities: Parameter Pipelined Version Non-Pipelined Version Clock Rate 500MHZ 350 MHz CPI for ALU 1 1 instructions CPI for 2 1 Control instructions CPI for 2.7 1 Memory instructions (a) For a program with 20% ALU instructions, 10% control instructions and 70% memory instructions, which design will be faster? Give a quantitative CPI average for each case. (b) For a program with 80% ALU instructions, 10% control instructions and 10% memory instructions, which design will be faster? Give a quantitative CPI average for each case