Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Just part D please, WILL RATE FAST! Please need help! 1. Design a BCD Adder that adds two BCD numbers (0 to 9) and produces

Just part D please, WILL RATE FAST! Please need help!

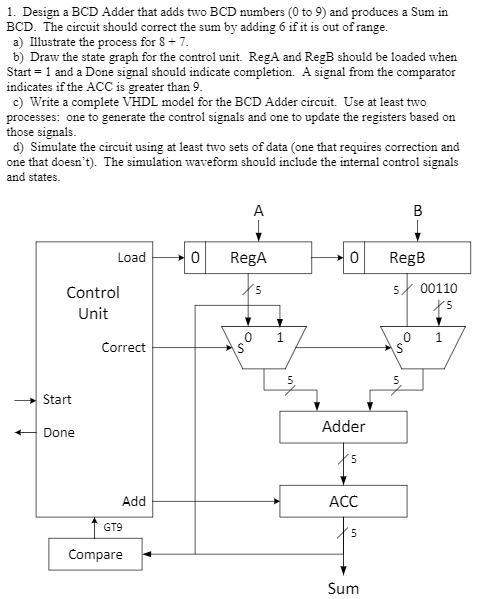

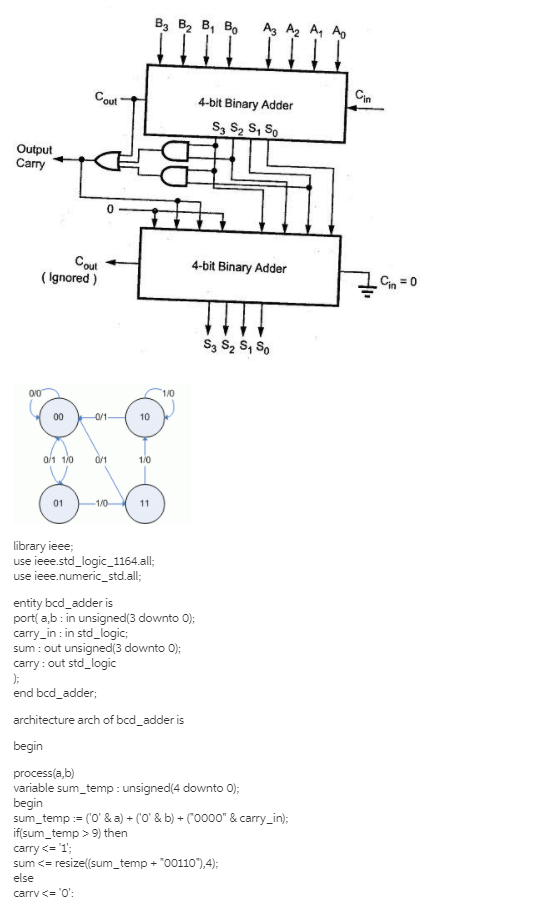

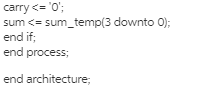

1. Design a BCD Adder that adds two BCD numbers (0 to 9) and produces a Sum in BCD. The circuit should correct the sum by adding 6 if it is out of range. a) Illustrate the process for 8-7. b) Draw the state graph for the control unit. RegA and RegB should be loaded when Start = 1 and a Done signal should indicate completion. A signal from the comparator indicates if the ACC is greater than 9. c) Write a complete VHDL model for the BCD Adder circuit. Use at least two processes: one to generate the control signals and one to update the registers based on those signals d) Simulate the circuit using at least two sets of data (one that requires correction and one that doesn't). The simulation waveform should include the internal control signals and states. A B Load 0 Rega 0 RegB 5 00110 Xs 5 Control Unit 1 0 S 1 Correct 0 S 5 5 Start Adder Done 5 Add ACC GT9 5 Compare Sum , , , Az A, A Cout Cin 4-bit Binary Adder S3 S2 S, Se Output Carry 777 gil '7 Cour 4-bit Binary Adder (Ignored) S, S, S, S, 010 1/0 00 0/1 10 0/1 1/0 0/1 1/0 01 -1/0 11 library ieee; use ieee.std_logic_1164.all; use ieee numeric_std.all; entity bcd_adder is port[a,b: in unsigned(3 downto 0); carry_in: in std_logic; sum: out unsigned(3 downto 0); carry: out std_logic ); end bcd_adder; architecture arch of bcd_adder is begin process(a,b) variable sum_temp: unsigned(4 downto 0); begin sum_temp := ('0' & a) + ('0' & b) + (0000" & carry_in); if(sum_temp>9) then carry 9) then carryStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started