Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Lab 4: Design Alternatives Design a circuit to multiply two 2-bit binary numbers, and display the results of the multiplication as a binary number, using

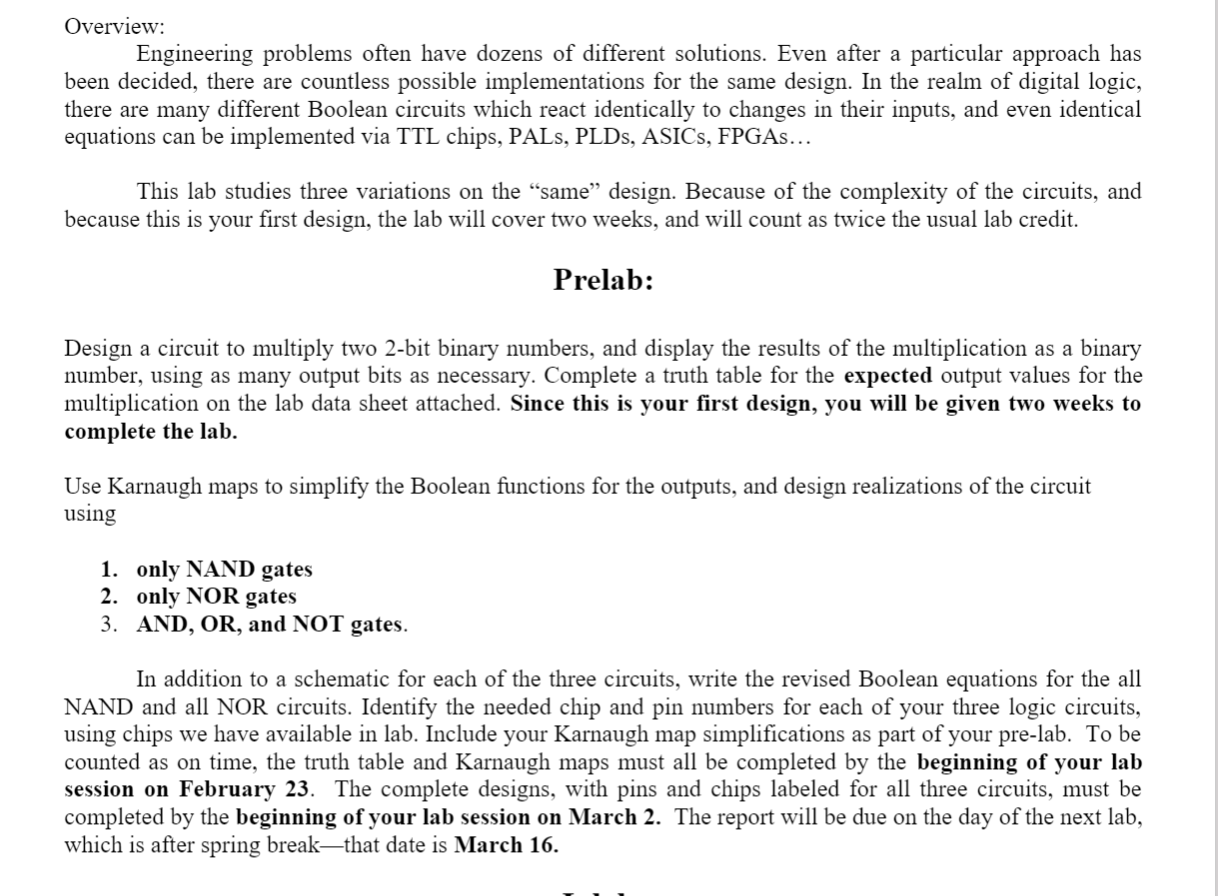

Lab 4: Design Alternatives

Design a circuit to multiply two 2-bit binary numbers, and display the results of the multiplication as a binary number, using as many output bits as necessary. Complete a truth table for the expected output values for the multiplication on the lab data sheet attached. Since this is your first design, you will be given two weeks to complete the lab.

Use Karnaugh maps to simplify the Boolean functions for the outputs, and design realizations of the circuit using.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started