Question: Lab on divide-by-n counters and registers. Having difficulty understanding registers as it is a new concept for me, instructions on how to complete procedures appreciated.

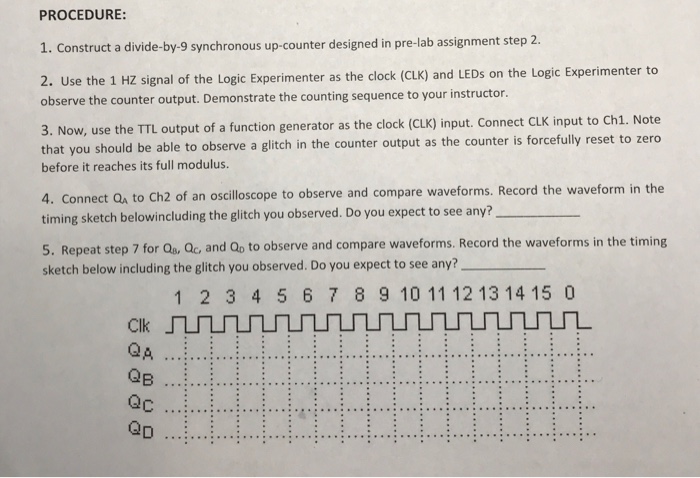

PROCEDURE: 1. Construct a divide-by-9 synchronous up-counter designed in pre-lab assignment step 2. 2. Use the 1 HZ signal of the Logic Experimenter as the clock (CLK) and LEDs on the Logic Experimenter to observe the counter output. Demonstrate the counting sequence to your instructor. Now, use the TTL output of a function generator as the clock (CLK) input, Connect CLK input to Ch1. Note that you should be able to observe a glitch in the counter output as the counter is forcefully re before it reaches its full modulus. set to zero 4. Connect Qa to Ch2 of an oscilloscope to observe and compare waveforms. Record the waveform in the timing sketch belowincluding the glitch you observed. Do you expect to see any? 5. Repeat step 7 for Qa, Qc, and Qp to observe and compare waveforms. Record the waveforms in the timing sketch below including the glitch you observed. Do you expect to see any? 1 2 345 67 8 9 10 11 12 13 14 150 Clk QA QD

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts