Question: Provide modulo-9 counter Verilog code for two pushbuttons, 4-digit 7 segment display: // Use this file as your 'lab3' project top level module // Your

Provide modulo-9 counter Verilog code for two pushbuttons, 4-digit 7 segment display:

![lab3 ( input logic clock, // 50 MHz clock output logic [3:0]](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66efdef466747_21266efdef403b2e.jpg)

![; logic [3:0] count[4] ; // counter values logic up[4], down[4] ;](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66efdef64530f_21366efdef5c8034.jpg)

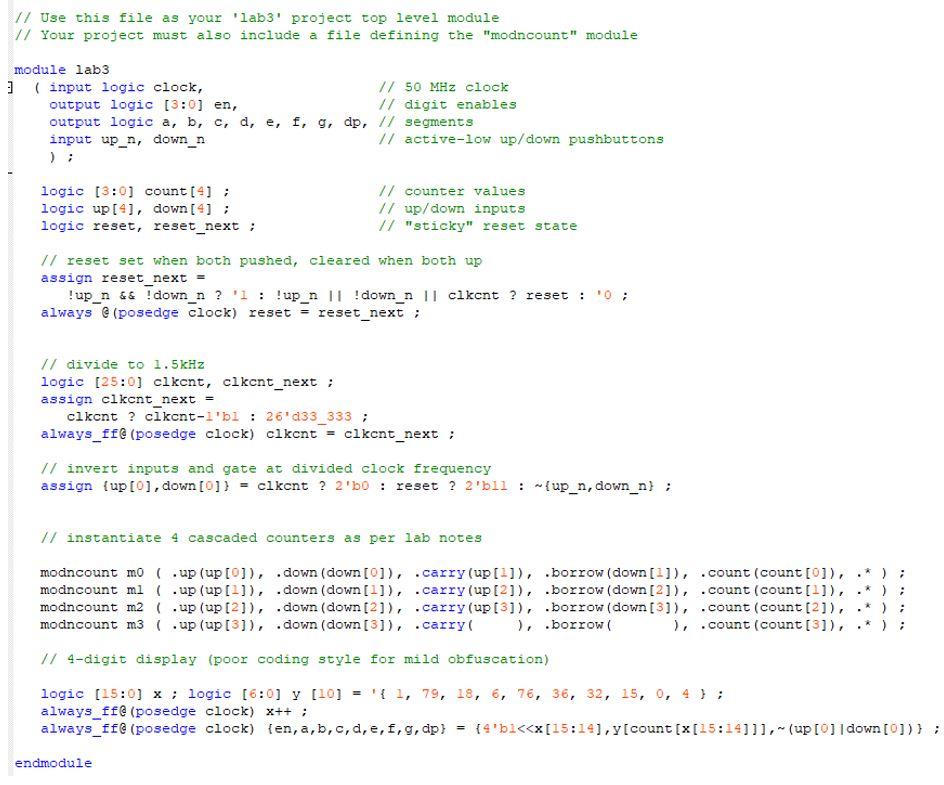

// Use this file as your 'lab3' project top level module // Your project must also include a file defining the "modncount" module

module lab3 ( input logic clock, // 50 MHz clock output logic [3:0] en, // digit enables output logic a, b, c, d, e, f, g, dp, // segments input up_n, down_n // active-low up/down pushbuttons ) ; logic [3:0] count[4] ; // counter values logic up[4], down[4] ; // up/down inputs logic reset, reset_next ; // "sticky" reset state

// reset set when both pushed, cleared when both up assign reset_next = !up_n && !down_n ? '1 : !up_n || !down_n || clkcnt ? reset : '0 ; always @(posedge clock) reset = reset_next ; // divide to 1.5kHz logic [25:0] clkcnt, clkcnt_next ; assign clkcnt_next = clkcnt ? clkcnt-1'b1 : 26'd33_333 ; always_ff@(posedge clock) clkcnt = clkcnt_next ; // invert inputs and gate at divided clock frequency assign {up[0],down[0]} = clkcnt ? 2'b0 : reset ? 2'b11 : ~{up_n,down_n} ;

// instantiate 4 cascaded counters as per lab notes

modncount m0 ( .up(up[0]), .down(down[0]), .carry(up[1]), .borrow(down[1]), .count(count[0]), .* ) ; modncount m1 ( .up(up[1]), .down(down[1]), .carry(up[2]), .borrow(down[2]), .count(count[1]), .* ) ; modncount m2 ( .up(up[2]), .down(down[2]), .carry(up[3]), .borrow(down[3]), .count(count[2]), .* ) ; modncount m3 ( .up(up[3]), .down(down[3]), .carry( ), .borrow( ), .count(count[3]), .* ) ; // 4-digit display (poor coding style for mild obfuscation) logic [15:0] x ; logic [6:0] y [10] = '{ 1, 79, 18, 6, 76, 36, 32, 15, 0, 4 } ; always_ff@(posedge clock) x++ ; always_ff@(posedge clock) {en,a,b,c,d,e,f,g,dp} = {4'b1

endmodule

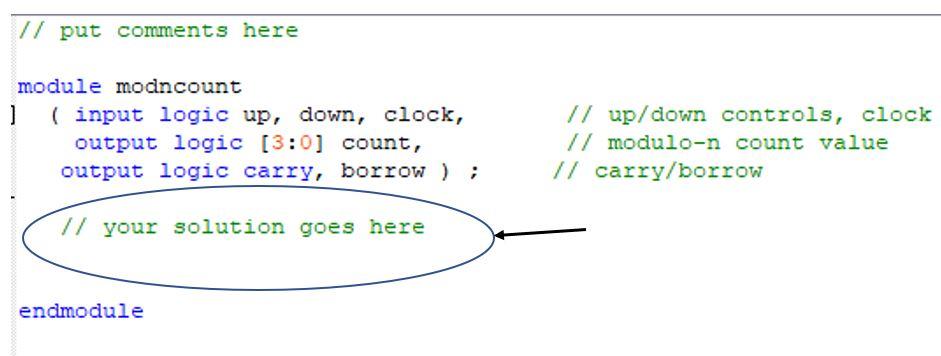

// put comments here

module modncount ( input logic up, down, clock, // up/down controls, clock output logic [3:0] count, // modulo-9 count value output logic carry, borrow ) ; // carry/borrow

// your solution goes here

endmodule

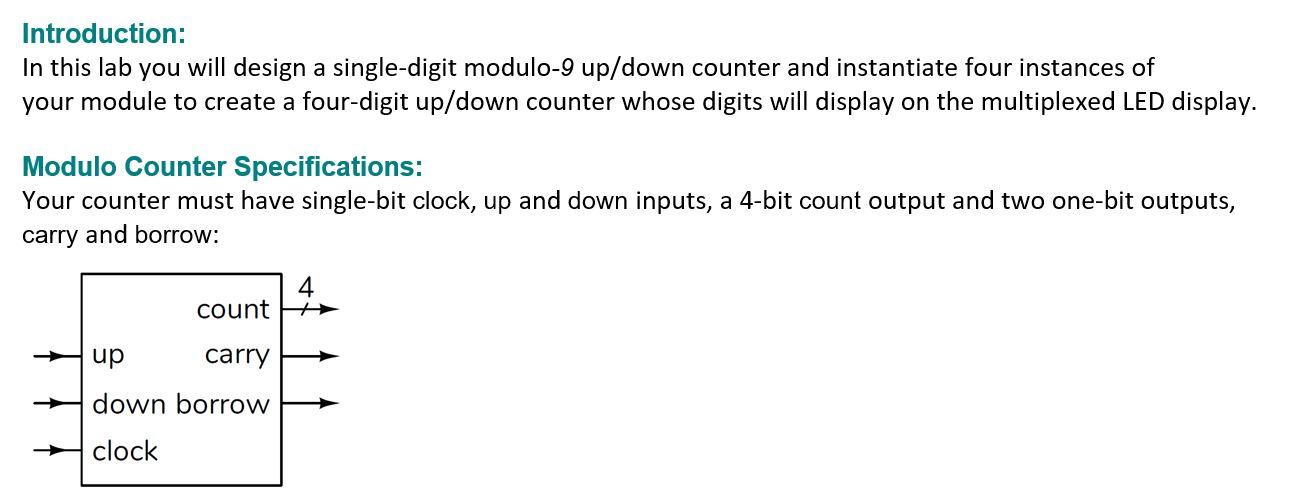

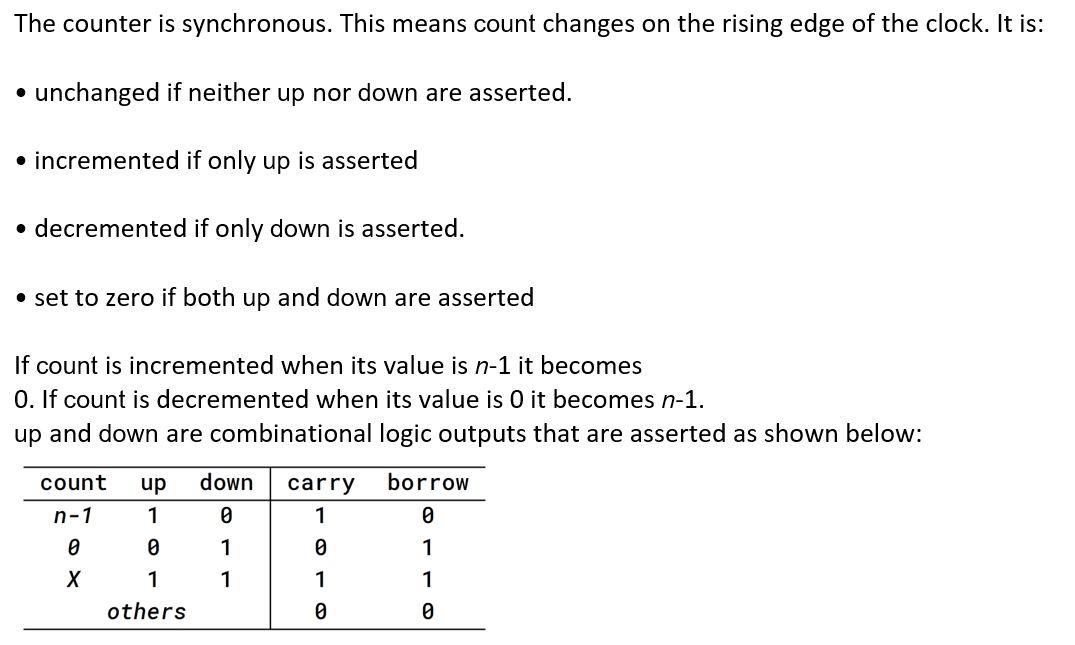

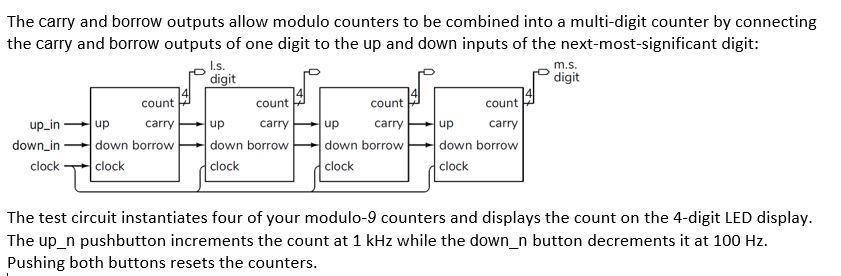

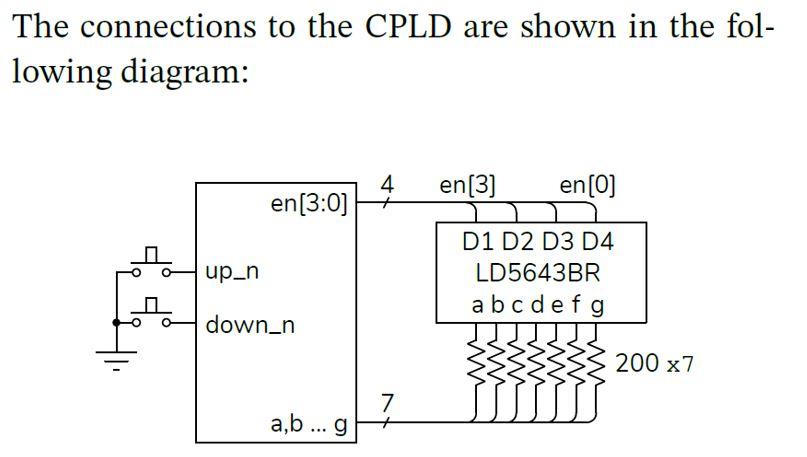

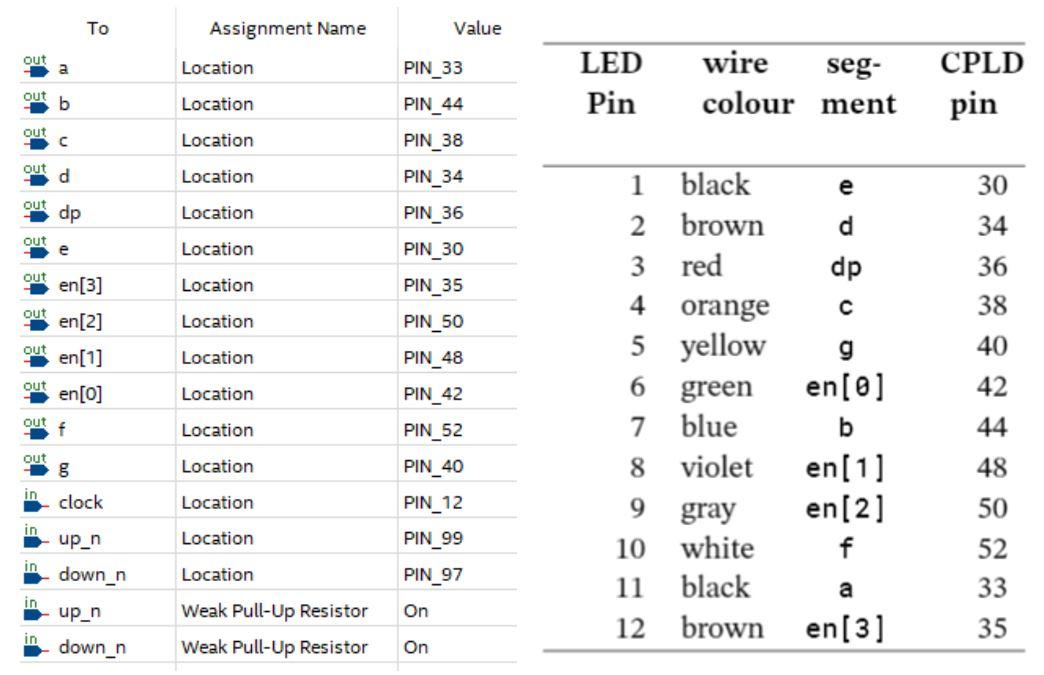

Introduction: In this lab you will design a single-digit modulo-9 up/down counter and instantiate four instances of your module to create a four-digit up/down counter whose digits will display on the multiplexed LED display. Modulo Counter Specifications: Your counter must have single-bit clock, up and down inputs, a 4-bit count output and two one-bit outputs, carry and borrow: 4 count H up carry down borrow clock The counter is synchronous. This means count changes on the rising edge of the clock. It is: unchanged if neither up nor down are asserted. incremented if only up is asserted decremented if only down is asserted. set to zero if both up and down are asserted If count is incremented when its value is n-1 it becomes 0. If count is decremented when its value is O it becomes n-1. up and down are combinational logic outputs that are asserted as shown below: count down up 1 carry 1 borrow 0 n-1 0 0 1 0 1 1 1 1 1 others 0 m.s. The carry and borrow outputs allow modulo counters to be combined into a multi-digit counter by connecting the carry and borrow outputs of one digit to the up and down inputs of the next-most-significant digit: I.s. digit digit count count count up_in up carry carry up carry carry down_in down borrow down borrow down borrow down borrow clock clock clock clock clock count up up The test circuit instantiates four of your modulo-9 counters and displays the count on the 4-digit LED display. The up_n pushbutton increments the count at 1 kHz while the down_n button decrements it at 100 Hz. Pushing both buttons resets the counters. 356S The connections to the CPLD are shown in the fol- lowing diagram: 4 en(3) en(0) en(3:0) up_n D1 D2 D3 D4 LD5643BR abcdefg down_n W w 200 x 7 W 7 ab... g To Assignment Name Value out a Location PIN_33 PIN_44 LED Pin wire seg. colour ment CPLD pin out Location out Location PIN_38 out d Location PIN_34 e out dp Location PIN_36 30 34 out e Location PIN_30 d dp 36 out en[3] Location PIN_35 out 38 en[2] Location PIN_50 PIN_48 1 black 2 brown 3 red 4 orange 5 yellow 6 green 7 blue 8 violet out 40 en[1] Location out en[O] Location PIN_42 42 out Location PIN_52 44 g en [ 0 ] b en[1] en [2] f out Location PIN_40 48 in clock Location PIN_12 9 gray in up_n Location PIN_99 PIN_97 50 52 33 in down_n 10 white 11 black 12 brown Location a in On 1. up_n down_n Weak Pull-Up Resistor Weak Pull-Up Resistor en[3] 35 On e 1 d2 dp 3 part number Uw 12 en[3] 11 a 10f 9 en[2] 8 en[1] 7 b top side of display en[0] 6 LD5643B // Use this file as your 'lab3' project top level module // Your project must also include a file defining the "modncount" module module lab3 : ( input logic clock, 7/ 50 MHz clock output logic (3:0) en, // digit enables output logic a, b, c, d, e, f, g, dp, // segments input up_n, down_n // active-low up/down pushbuttons logic (3:0) count(4) ; logic up[4], down[4]; logic reset, reset_next; // counter values // up/down inputs // "sticky" reset state // reset set when both pushed, cleared when both up assign reset_next = ! up_n && !down_n ? '1 : !up_n || ! down_n 11 clkent ? reset : ' ; always @ (posedge clock) reset = reset_next; // divide to 1.5kHz logic (25:0) clkent, clkcnt_next ; assign clkcnt_next = clkcnt ? clkcnt-l'bi : 26'd33_333; always_ff@ (posedge clock) clkent = clkcnt_next; // invert inputs and gate at divided clock frequency assign {up [0], down[0]) = clkent ? 2'bo : reset ? 2'bll : ~{up_n, down_n) ; // instantiate 4 cascaded counters as per lab notes : modncount mo ( .up (up[0]), .down (down[0]), .carry(up[1]), .borrow (down[1]), .count (count[0), .*) modncount ml ( .up (up[-]), down (down[1]), .carry (up [2]), borrow (down[2]), .count (count [1]), .*); modncount m2 ( .up (up [2]), .down (down (21), .carry(up [3]), .borrow (down (31), .count (count [2]), > ; modncount m3 ( .up (up [3]), .down (down[3]), .carry ), borrow ), .count (count [3]), 1/4-digit display (poor coding style for mild obfuscation) logic (15:0] x ; logic [6:0] Y [10] = '{ 1, 79, 18, 6, 76, 36, 32, 15, 0, 4); always_ff@ (posedge clock) x++; always_ff@ (posedge clock) (en, a, b, c, d, e, f, g, dp) = {4'bi ; modncount m3 ( .up (up [3]), .down (down[3]), .carry ), borrow ), .count (count [3]), 1/4-digit display (poor coding style for mild obfuscation) logic (15:0] x ; logic [6:0] Y [10] = '{ 1, 79, 18, 6, 76, 36, 32, 15, 0, 4); always_ff@ (posedge clock) x++; always_ff@ (posedge clock) (en, a, b, c, d, e, f, g, dp) = {4'bi

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts