Answered step by step

Verified Expert Solution

Question

1 Approved Answer

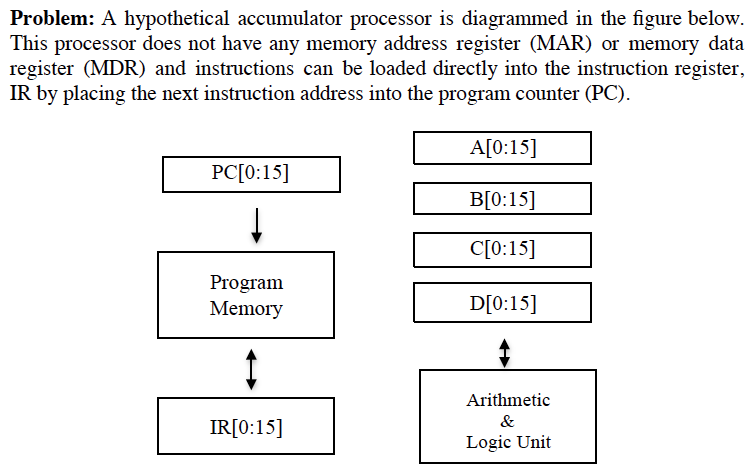

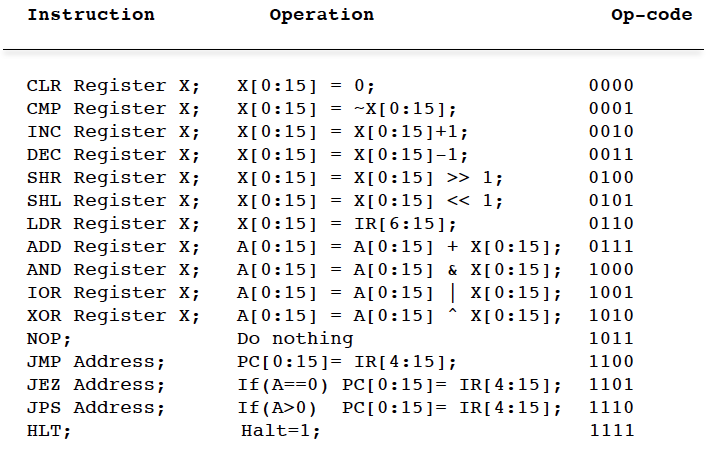

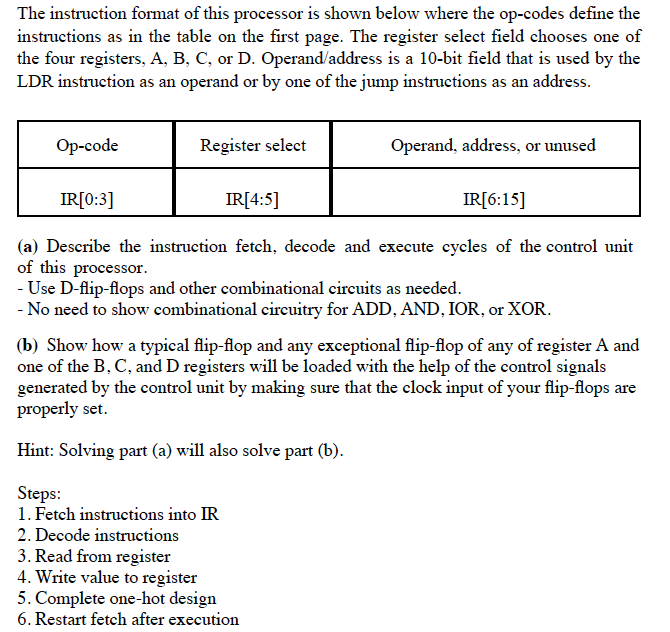

Let me know if you have any questions! Thanks =) Problem: A hypothetical accumulator processor is diagrammed in the figure below This processor does not

Let me know if you have any questions! Thanks =)

Problem: A hypothetical accumulator processor is diagrammed in the figure below This processor does not have any memory address register (MAR) or memory data register (MDR) and instructions can be loaded directly into the instruction register, IR by placing the next instruction address into the program counter (PC) A[0:15] B[0:15] C[0:15] D[0:15] PC[0:15] Program Memory Arithmetic IR[0:15] Logic Unit Instruction Operation Op-code CLR Register X; X[ 0:15] = 0; CHP Register x; X [ 0 : 15 ] ~X [ 0 :151 ; INC Register x; X[ 0:15] X[ 0:15]+1; DEC Register X; X[0 15X[0:151-1; SHR Register x; X[ 0:15] = X[ 0:15] >> 1; SHL Register x; X[ 0:15] X[ 0:15] 0 PCI0:15] IRI4:15] 1110 Halt-l The instruction format of this processor is shown below where the op-codes define the instructions as in the table on the first page. The register select field chooses one of the four registers, A, B. C, or D. Operand/address is a 10-bit field that is used by the LDR instruction as an operand or by one of the jump instructions as an address Op-code Register select Operand, address, or unused IR[0:3] IR[4:5] IR[6:15] (a) Describe the instruction fetch, decode and execute cycles of the control unit of this processor - Use D-flip-flops and other combinational circuits as needed - No need to show combinational circuitry for ADD, AND. IOR, or XOR (b) Show how a typical flip-flop and any exceptional flip-flop of any of register A and one of the B. C, and D registers will be loaded with the help of the control signals generated by the control unit by making sure that the clock input of your flip-flops are properly set Hint: Solving part (a) will also solve part (b) Steps 1. Fetch instructions into IR 2. Decode instructions 3. Read from register 4. Write value to register 5. Complete one-hot design 6. Restart fetch after execution Problem: A hypothetical accumulator processor is diagrammed in the figure below This processor does not have any memory address register (MAR) or memory data register (MDR) and instructions can be loaded directly into the instruction register, IR by placing the next instruction address into the program counter (PC) A[0:15] B[0:15] C[0:15] D[0:15] PC[0:15] Program Memory Arithmetic IR[0:15] Logic Unit Instruction Operation Op-code CLR Register X; X[ 0:15] = 0; CHP Register x; X [ 0 : 15 ] ~X [ 0 :151 ; INC Register x; X[ 0:15] X[ 0:15]+1; DEC Register X; X[0 15X[0:151-1; SHR Register x; X[ 0:15] = X[ 0:15] >> 1; SHL Register x; X[ 0:15] X[ 0:15] 0 PCI0:15] IRI4:15] 1110 Halt-l The instruction format of this processor is shown below where the op-codes define the instructions as in the table on the first page. The register select field chooses one of the four registers, A, B. C, or D. Operand/address is a 10-bit field that is used by the LDR instruction as an operand or by one of the jump instructions as an address Op-code Register select Operand, address, or unused IR[0:3] IR[4:5] IR[6:15] (a) Describe the instruction fetch, decode and execute cycles of the control unit of this processor - Use D-flip-flops and other combinational circuits as needed - No need to show combinational circuitry for ADD, AND. IOR, or XOR (b) Show how a typical flip-flop and any exceptional flip-flop of any of register A and one of the B. C, and D registers will be loaded with the help of the control signals generated by the control unit by making sure that the clock input of your flip-flops are properly set Hint: Solving part (a) will also solve part (b) Steps 1. Fetch instructions into IR 2. Decode instructions 3. Read from register 4. Write value to register 5. Complete one-hot design 6. Restart fetch after executionStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started