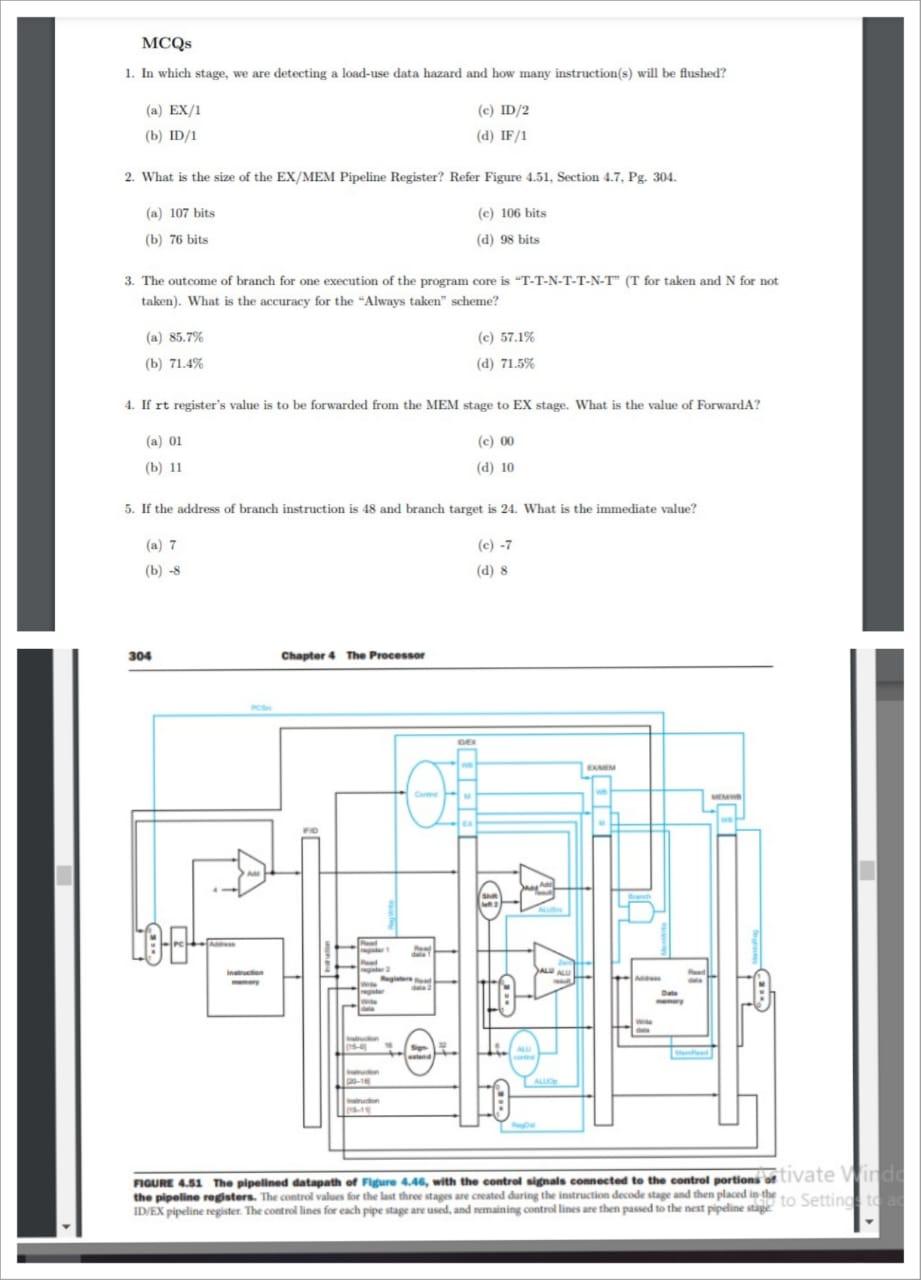

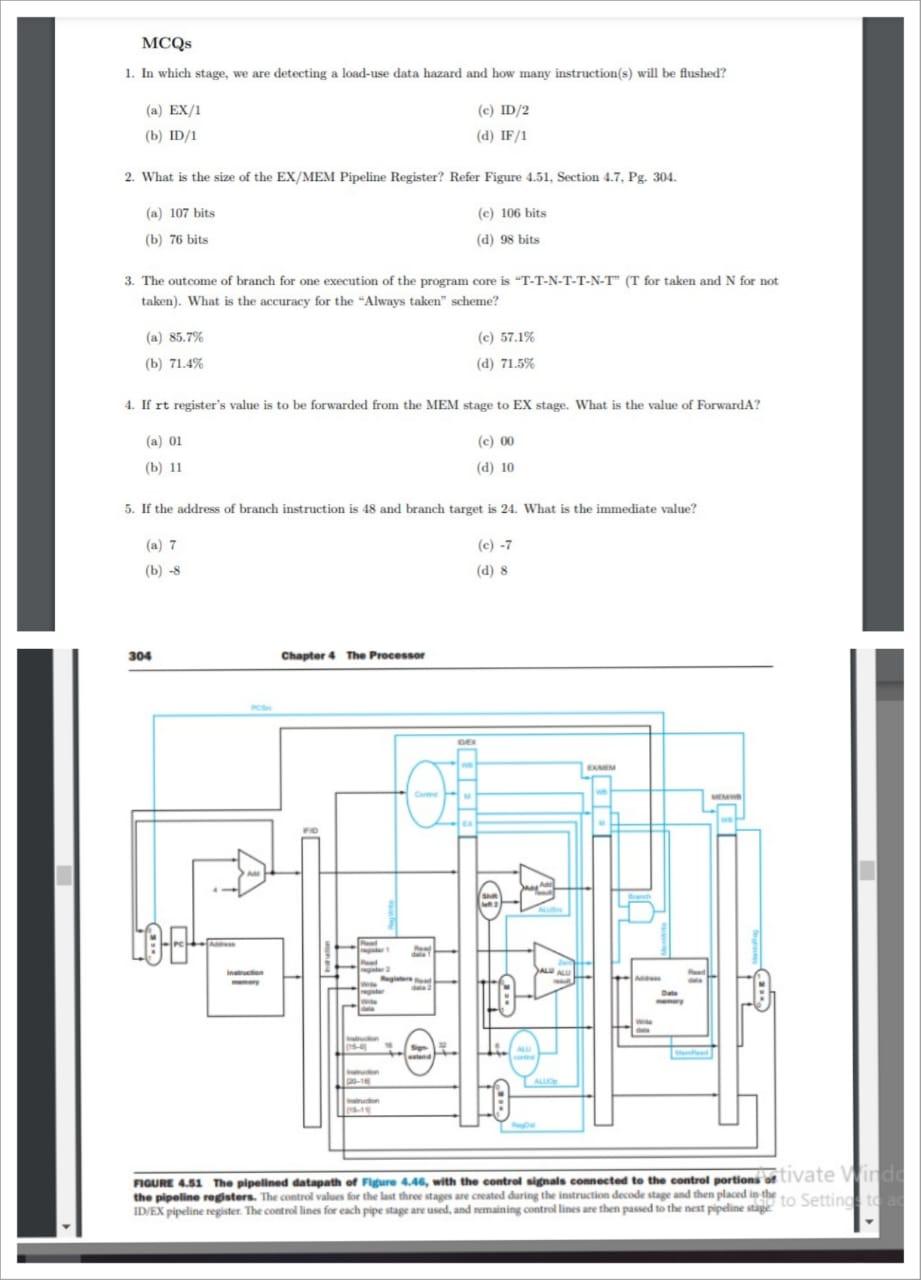

MCQs 1. In which stage, we are detecting a load-use data hazard and how many instruction(s) will be flushed? (a) EX/1 (b) ID/1 (e) ID/2 (d) IF/1 2. What is the size of the EX/MEM Pipeline Register? Refer Figure 4.51, Section 4.7. Pg. 304. (c) 106 bits (a) 107 bits (b) 76 bits (d) 98 bits 3. The outcome of branch for one execution of the program core is "T-T-N-T-T-N-T (T for taken and N for not taken). What is the accuracy for the "Always taken" scheme? (a) 85.7% (c) 57.1% (b) 71.4% (d) 71.5% 4. If rt register's value is to be forwarded from the MEM stage to EX stage. What is the value of ForwardA? (a) 01 (c) 00 (b) 11 (d) 10 5. If the address of branch instruction is 48 and branch target is 24. What is the immediate value? (a) 7 (b) -8 (c) -7 (d) 8 304 Chapter 4 The Processor o Lo FIGURE 4.51 The pipelined datapath of Figure 6.46, with the control signats connected to the control portions of tivated the pipeline registers. The control values for the last three stages are created during the instruction decode stage and then placed in the to Setting ID/EX pipeline register. The control lines for each pipe stage are used and remaining control lines are then paused to the nest pipeline stage MCQs 1. In which stage, we are detecting a load-use data hazard and how many instruction(s) will be flushed? (a) EX/1 (b) ID/1 (e) ID/2 (d) IF/1 2. What is the size of the EX/MEM Pipeline Register? Refer Figure 4.51, Section 4.7. Pg. 304. (c) 106 bits (a) 107 bits (b) 76 bits (d) 98 bits 3. The outcome of branch for one execution of the program core is "T-T-N-T-T-N-T (T for taken and N for not taken). What is the accuracy for the "Always taken" scheme? (a) 85.7% (c) 57.1% (b) 71.4% (d) 71.5% 4. If rt register's value is to be forwarded from the MEM stage to EX stage. What is the value of ForwardA? (a) 01 (c) 00 (b) 11 (d) 10 5. If the address of branch instruction is 48 and branch target is 24. What is the immediate value? (a) 7 (b) -8 (c) -7 (d) 8 304 Chapter 4 The Processor o Lo FIGURE 4.51 The pipelined datapath of Figure 6.46, with the control signats connected to the control portions of tivated the pipeline registers. The control values for the last three stages are created during the instruction decode stage and then placed in the to Setting ID/EX pipeline register. The control lines for each pipe stage are used and remaining control lines are then paused to the nest pipeline stage