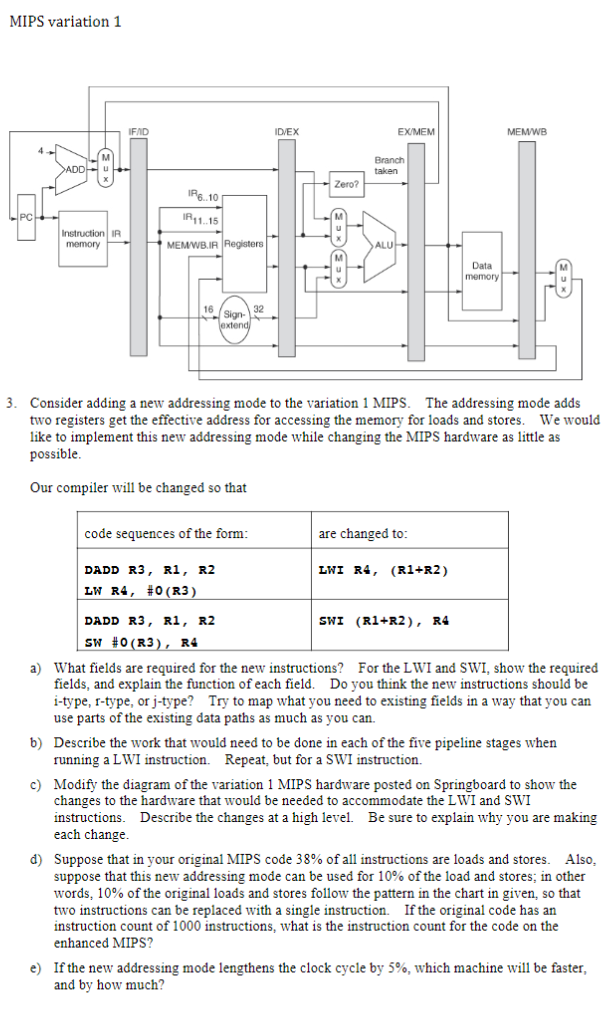

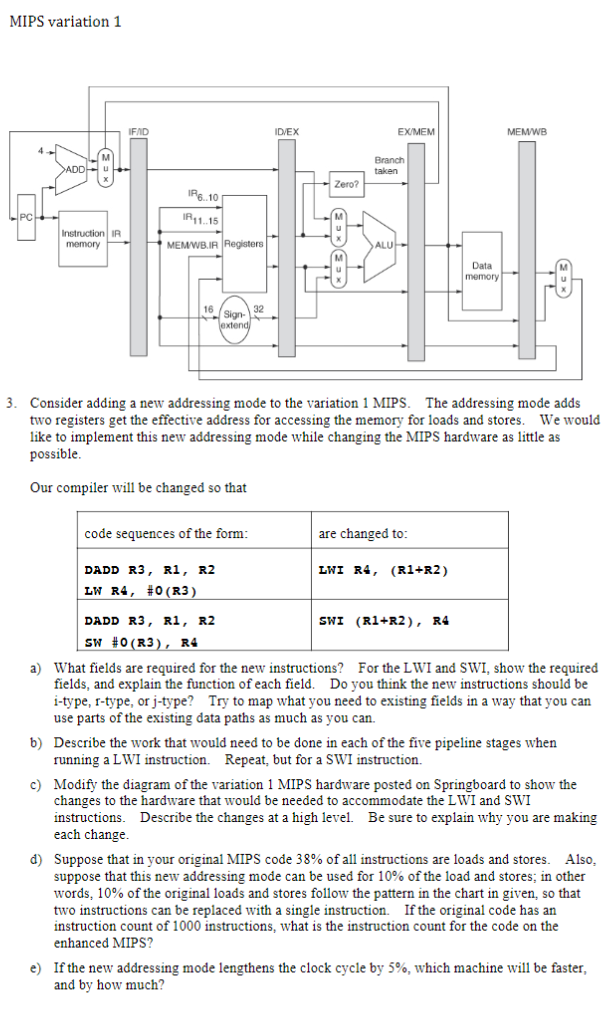

MIPS variation 1 FAD DVEX EXMEM MEMWE Branch er0ken PC R111 Instruction IR memory MEMWB.IR Registers ALU Data memory 6 sig 32 3. The addressing mode adds Consider adding a new addressing mode to the variation 1 MIPS. two registers get the effective address for accessing the memory for loads and stores. We would like to implement this new addressing mode while changing the MIPS hardware as little as possible 1 Our compiler will be changed so that code sequences of the form DADD R3, R1, R2 LM R4, #0(R3) DADD R3, R1, R2 sw #0(R3), R4 are changed to LWI R4, (Rl+R2) Sw1 (R1+R2), R4 a) For the LWI and SWI, show the required What fields are required for the new instructions? fields, and explain the function of each field. Do you think the new instructions should be i-type, r-type, or j-type? Try to map what you need to existing fields in a way that you can use parts of the existing data paths as much as you can. b) Describe the work that would need to be done in each of the five pipeline stages when running a L WI instruction. Repeat, but for a SWI instruction c) Modify the diagram of the variation 1 MIPS hardware posted on Springboard to show the changes to the hardware that would be needed to accommodate the LWI and SWI instructions. Describe the changes at a high level. Be sure to explain why you are making each change d) Also Suppose that in your original MIPS code 38% of all instructions are loads and stores. suppose that this new addressing mode can be used for 10% of the load and stores, in other words, 10% of the original loads and stores follow the pattern in the chart in given, so that two instructions can be replaced with a single instruction. If the original code has an instruction count of 1000 instructions, what is the instruction count for the code on the enhanced MIPS? If the new addressing mode lengthens the clock cycle by 5%, which machine will be faster and by how much? e) MIPS variation 1 FAD DVEX EXMEM MEMWE Branch er0ken PC R111 Instruction IR memory MEMWB.IR Registers ALU Data memory 6 sig 32 3. The addressing mode adds Consider adding a new addressing mode to the variation 1 MIPS. two registers get the effective address for accessing the memory for loads and stores. We would like to implement this new addressing mode while changing the MIPS hardware as little as possible 1 Our compiler will be changed so that code sequences of the form DADD R3, R1, R2 LM R4, #0(R3) DADD R3, R1, R2 sw #0(R3), R4 are changed to LWI R4, (Rl+R2) Sw1 (R1+R2), R4 a) For the LWI and SWI, show the required What fields are required for the new instructions? fields, and explain the function of each field. Do you think the new instructions should be i-type, r-type, or j-type? Try to map what you need to existing fields in a way that you can use parts of the existing data paths as much as you can. b) Describe the work that would need to be done in each of the five pipeline stages when running a L WI instruction. Repeat, but for a SWI instruction c) Modify the diagram of the variation 1 MIPS hardware posted on Springboard to show the changes to the hardware that would be needed to accommodate the LWI and SWI instructions. Describe the changes at a high level. Be sure to explain why you are making each change d) Also Suppose that in your original MIPS code 38% of all instructions are loads and stores. suppose that this new addressing mode can be used for 10% of the load and stores, in other words, 10% of the original loads and stores follow the pattern in the chart in given, so that two instructions can be replaced with a single instruction. If the original code has an instruction count of 1000 instructions, what is the instruction count for the code on the enhanced MIPS? If the new addressing mode lengthens the clock cycle by 5%, which machine will be faster and by how much? e)