Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Module 2 . Pipeline Enhancement In this project, you are provided with an architecture presented in a PowerPoint file format ( m 2 _ pipeline.pptx

Module Pipeline Enhancement

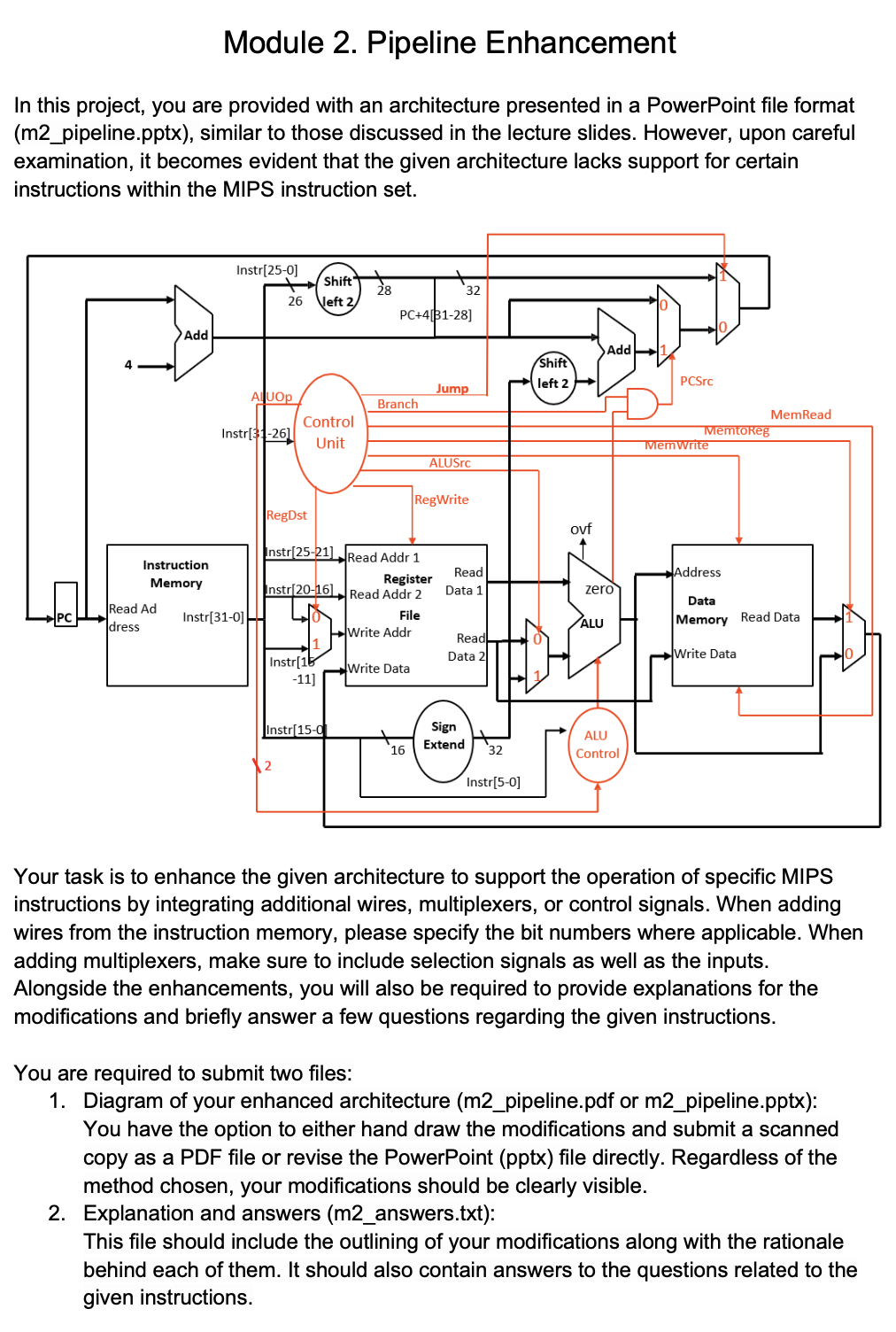

In this project, you are provided with an architecture presented in a PowerPoint file format mpipeline.pptx similar to those discussed in the lecture slides. However, upon careful examination, it becomes evident that the given architecture lacks support for certain instructions within the MIPS instruction set. Your task is to enhance the given architecture to support the operation of specific MIPS instructions by integrating additional wires, multiplexers, or control signals. When adding wires from the instruction memory, please specify the bit numbers where applicable. When adding multiplexers, make sure to include selection signals as well as the inputs. Alongside the enhancements, you will also be required to provide explanations for the modifications and briefly answer a few questions regarding the given instructions.

You are required to submit two files:Diagram of your enhanced architecture mpipeline.pdf or mpipeline.pptx:You have the option to either hand draw the modifications and submit a scannedcopy as a PDF file or revise the PowerPoint pptx file directly. Regardless of themethod chosen, your modifications should be clearly visible.Explanation and answers manswers.txt:This file should include the outlining of your modifications along with the rationalebehind each of them. It should also contain answers to the questions related to thegiven instructions.

The current architecture is unable to execute the jr instruction. Please make appropriate modifications to the architecture to enable the operation and answer the following questions.

instruction format: jr RS sample instruction: jr $

OPCODE RS RT RD SHAMT FUNCT

Q Why is the jr instruction not classified as a Jtype instruction?

Q What rationale could explain why the jr instruction is not categorized as an Itype instruction?

The current architecture is unable to execute the sll Shift Left Logical instruction. Please make appropriate modifications to the architecture to enable the operation and answer the following questions. You may assume that the ALU takes two operands, source register and shift amount, to perform the shift operation.

instruction format: sll RD RT SHAMT sample instruction: sll $ $

OPCODE RS RT RD SHAMT FUNCT

Q What factors might explain the choice of $rt over $rs as the source register for the sll instruction?

Q What could be some reasons why shift operations utilize shamt as the operand instead of using two source registers?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started