Answered step by step

Verified Expert Solution

Question

1 Approved Answer

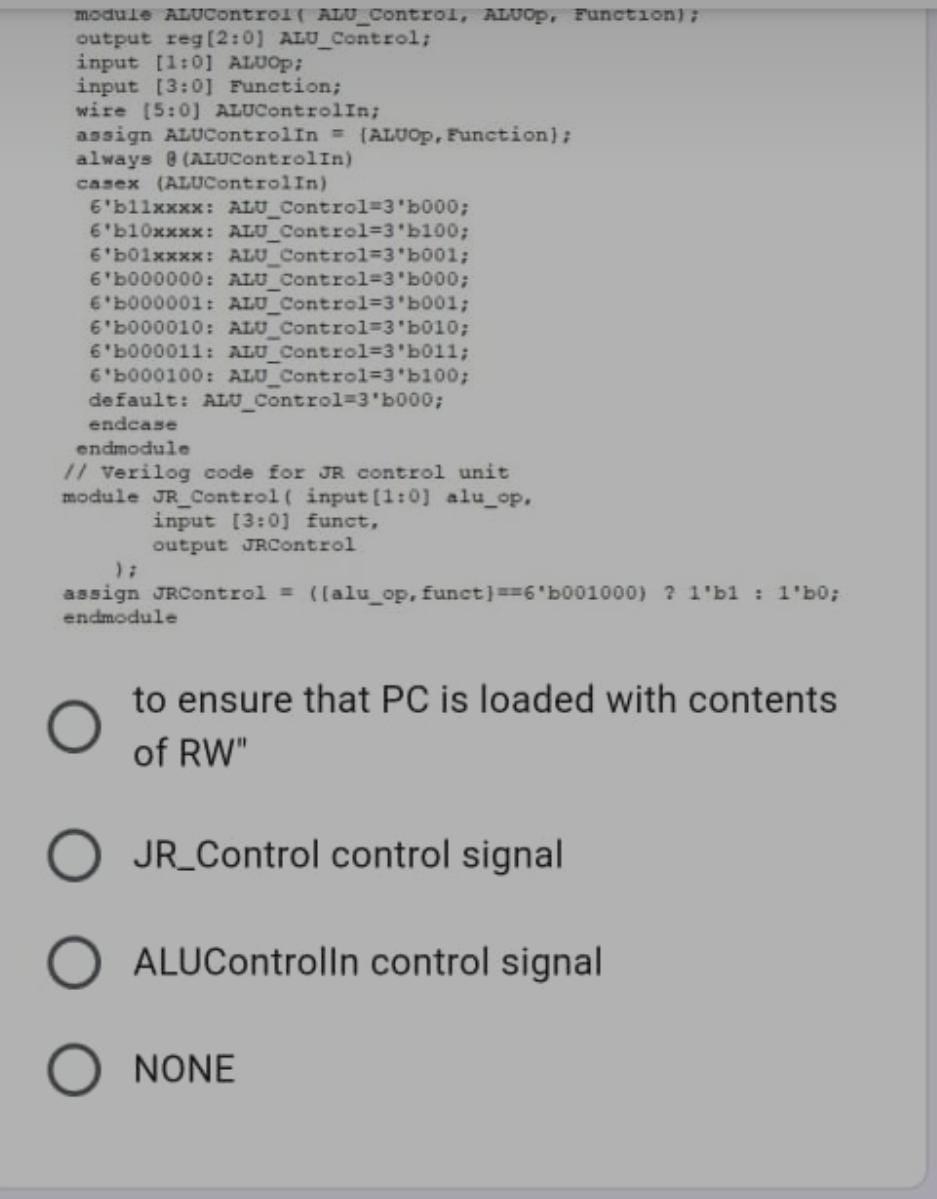

module ALUControl( ALU Control, ALUOP, Function); output reg[2:0] ALU Control; input [1:01 ALUOP: input [3:0] Function; wire [5:0] ALUControlIn; assign ALUControlin = (ALUOP, Function);

module ALUControl( ALU Control, ALUOP, Function); output reg[2:0] ALU Control; input [1:01 ALUOP: input [3:0] Function; wire [5:0] ALUControlIn; assign ALUControlin = (ALUOP, Function); always @ (ALUControlIn) casex (ALUControlIn) 6'bllxxxx: ALU_Control=D3'b000; 6'b10xxxx: ALU_Control=3 b100; 6'b01xxxx: ALU Control%3D3'b001; 6'b000000: ALU Control%3D3'b000; 6'b000001: ALU Control=3'b001; 6'b000010: ALU Control=3'b010; 6 b000011: ALU Control%3D3'b011; 6'b000100: ALU Control3D3 b100; default: ALU_Control=3'b000; endcase endmodule // Verilog code for JR control unit module JR Control ( input [1:0] alu op, input [3:0] funct, output JRControl assign JRControl = ([alu_op, funct)==6'b001000) ? 1'b1 : 1'b0; endmodule to ensure that PC is loaded with contents of RW" JR_Control control signal ALUControlln control signal O NONE

Step by Step Solution

★★★★★

3.41 Rating (151 Votes )

There are 3 Steps involved in it

Step: 1

option a will be right ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started