Question: Need help in Operating Systems. We use Simulator paging-multilevel-translate.py to study how the address translation work with the multi-level paging table. We ran a configuration

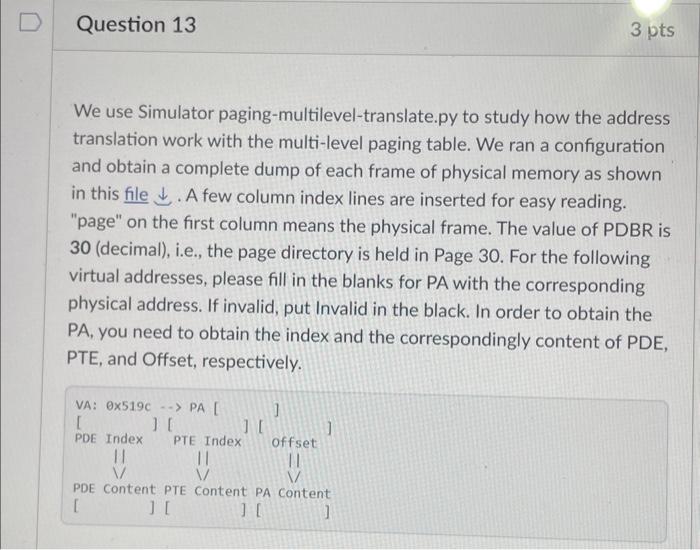

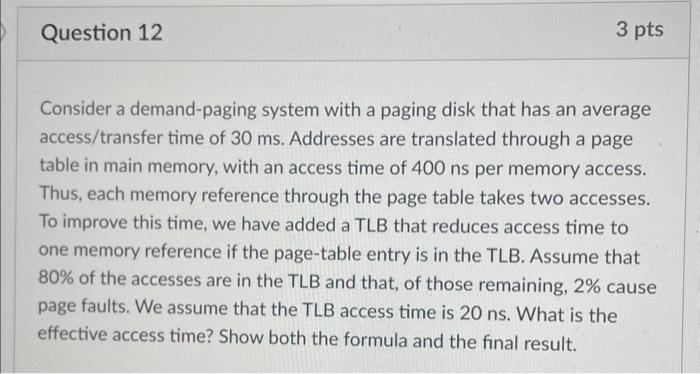

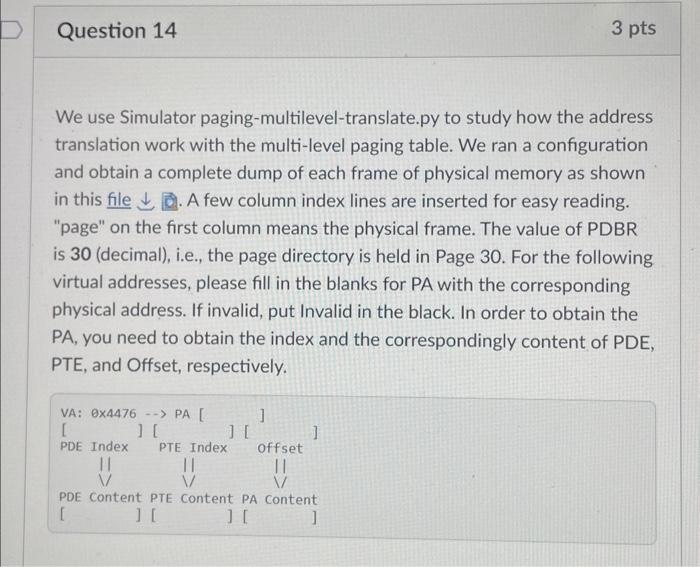

We use Simulator paging-multilevel-translate.py to study how the address translation work with the multi-level paging table. We ran a configuration and obtain a complete dump of each frame of physical memory as shown in this file . A few column index lines are inserted for easy reading. "page" on the first column means the physical frame. The value of PDBR is 30 (decimal), i.e., the page directory is held in Page 30 . For the following virtual addresses, please fill in the blanks for PA with the corresponding physical address. If invalid, put Invalid in the black. In order to obtain the PA, you need to obtain the index and the correspondingly content of PDE, PTE, and Offset, respectively. Consider a demand-paging system with a paging disk that has an average access/transfer time of 30ms. Addresses are translated through a page table in main memory, with an access time of 400 ns per memory access. Thus, each memory reference through the page table takes two accesses. To improve this time, we have added a TLB that reduces access time to one memory reference if the page-table entry is in the TLB. Assume that 80% of the accesses are in the TLB and that, of those remaining, 2% cause page faults. We assume that the TLB access time is 20ns. What is the effective access time? Show both the formula and the final result. We use Simulator paging-multilevel-translate.py to study how the address translation work with the multi-level paging table. We ran a configuration and obtain a complete dump of each frame of physical memory as shown in this file 0. A few column index lines are inserted for easy reading. "page" on the first column means the physical frame. The value of PDBR is 30 (decimal), i.e., the page directory is held in Page 30 . For the following virtual addresses, please fill in the blanks for PA with the corresponding physical address. If invalid, put Invalid in the black. In order to obtain the PA, you need to obtain the index and the correspondingly content of PDE, PTE, and Offset, respectively

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts