Question

Objective : Using Quartus design and test an 8-bit Right shift register with serial input. Use D flip-flops (FF)in your design (Libraries: primitives Storage dff).

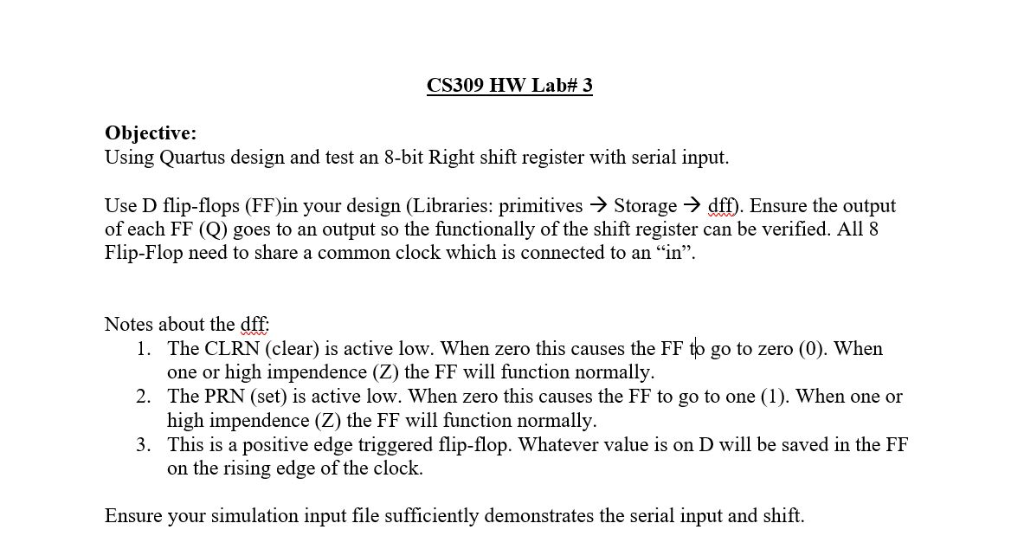

Objective:

Using Quartus design and test an 8-bit Right shift register with serial input. Use D flip-flops (FF)in your design (Libraries: primitives Storage dff). Ensure the output of each FF (Q) goes to an output so the functionally of the shift register can be verified. All 8 Flip-Flop need to share a common clock which is connected to an in.

Notes about the dff:

1. The CLRN (clear) is active low. When zero this causes the FF to go to zero (0). When one or high impendence (Z) the FF will function normally.

2. The PRN (set) is active low. When zero this causes the FF to go to one (1). When one or high impendence (Z) the FF will function normally.

3. This is a positive edge triggered flip-flop. Whatever value is on D will be saved in the FF on the rising edge of the clock.

Ensure your simulation input file correctly demonstrates the serial input and shift.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started