Question

Objectives: Learn how to represent hardware combinational logic, including adders, in truth tables and logic equations, how to minimize logic using a Karnaugh map, and

Objectives: Learn how to represent hardware combinational logic, including adders, in truth tables and logic equations, how to minimize logic using a Karnaugh map, and how to represent and test hardware logic using the Verilog hardware description language and simulator. Submit your file through the Blackboard Assignment Portal for this class.

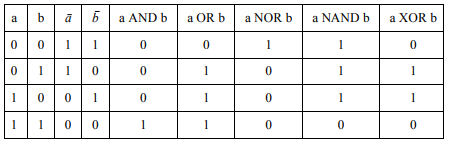

Consider the following truth table.

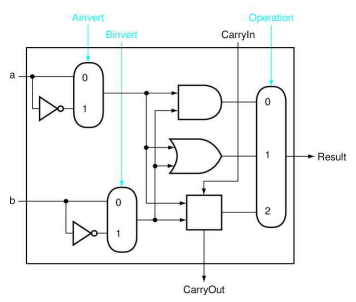

Also consider the following 1-bit ALU that performs AND, OR, and addition on a and b.

Assume that the Ainvert and Binvert signals can be asserted or deasserted and that the CarryIn signal can be deasserted or taken from the CarryOut of the preceding 1-bit ALU. The value of a NOR b can be obtained by asserting Ainvert and Binvert and selecting an AND operation.

(a) Describe how the value of a NAND b can be obtained.

(b) Describe how the value of a XOR b can be obtained.

a ba AND ba OR ba NOR ba NAND b a XOR b 0 01 1 001 0 a ba AND ba OR ba NOR ba NAND b a XOR b 0 01 1 001 0Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started