Question

ONLY USING VHDL FORMAT PLEASE DO NOT USE VERILOG library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; use ieee.NUMERIC_STD.all; ----------------------------------------------- ---------- ALU 8-bit VHDL --------------------- ----------------------------------------------- entity

ONLY USING VHDL FORMAT PLEASE DO NOT USE VERILOG

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; use ieee.NUMERIC_STD.all; ----------------------------------------------- ---------- ALU 8-bit VHDL --------------------- ----------------------------------------------- entity ALU is generic ( constant N: natural := 1 -- number of shited or rotated bits ); Port ( A, B : in STD_LOGIC_VECTOR(7 downto 0); -- 2 inputs 8-bit ALU_Sel : in STD_LOGIC_VECTOR(3 downto 0); -- 1 input 4-bit for selecting function ALU_Out : out STD_LOGIC_VECTOR(7 downto 0); -- 1 output 8-bit Carryout : out std_logic -- Carryout flag ); end ALU; architecture Behavioral of ALU is

signal ALU_Result : std_logic_vector (7 downto 0); signal tmp: std_logic_vector (8 downto 0);

begin process(A,B,ALU_Sel) begin case(ALU_Sel) is when "0000" => -- Addition ALU_Result -- Subtraction ALU_Result -- Multiplication ALU_Result -- Division ALU_Result -- Logical shift left ALU_Result -- Logical shift right ALU_Result -- Rotate left ALU_Result -- Rotate right ALU_Result -- Logical and ALU_Result -- Logical or ALU_Result -- Logical xor ALU_Result -- Logical nor ALU_Result -- Logical nand ALU_Result -- Logical xnor ALU_Result -- Greater comparison if(A>B) then ALU_Result -- Equal comparison if(A=B) then ALU_Result ALU_Result

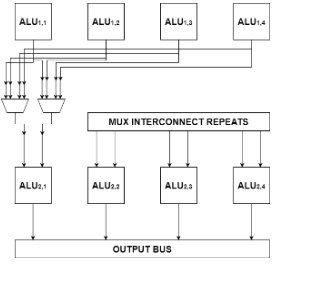

USE THE ALU ABOVE TO ANSWER THIS QUESTION. In the block diagram given below inputs are fed into the first row of ALU blocks as shown. Each of the

inputs to the ALUs are 8-bit wide. Program / Configure the ALUs in such a way that the

ALU(1,1) performs a NAND, ALU(1,2) performs a NOR, ALU(1,3) performs an AND,

and ALU(1,4) performs an OR. Program the ALUs in the second row with the following

operations: ALU(2,1) performs an Addition, ALU(2,2) performs a Logical Right Shift,

ALU(2,3) performs an Arithmetic Right Shift, and ALU(2,4) performs a Subtraction. For

this question, use the MUX based interconnect as shown in the block diagram. PLEASE INCLUDE YOUR TEST BENCH

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started