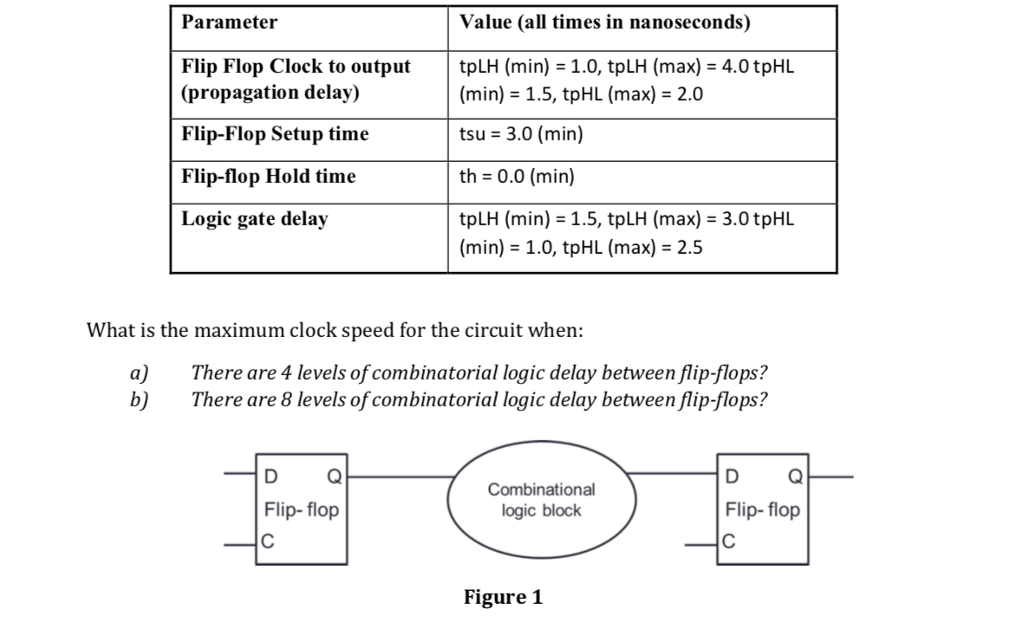

Question: Parameter Value (all times in nanoseconds) Flip Flop Clock to output (propagation delay) tpLH (min) = 1.0, tpLH (max) = 4.0 tpHL (min) = 1.5,

Parameter Value (all times in nanoseconds) Flip Flop Clock to output (propagation delay) tpLH (min) = 1.0, tpLH (max) = 4.0 tpHL (min) = 1.5, tpHL (max) = 2.0 Flip-Flop Setup time tsu = 3.0 (min) Flip-flop Hold time th = 0.0 (min) Logic gate delay tpLH (min) = 1.5, tpLH (max) = 3.0 tpHL (min) = 1.0, tpHL (max) = 2.5 What is the maximum clock speed for the circuit when: a) b) There are 4 levels of combinatorial logic delay between flip-flops? There are 8 levels of combinatorial logic delay between flip-flops? D QH Flip-flop Combinational logic block HOH D Q Flip-flop Figure 1 Parameter Value (all times in nanoseconds) Flip Flop Clock to output (propagation delay) tpLH (min) = 1.0, tpLH (max) = 4.0 tpHL (min) = 1.5, tpHL (max) = 2.0 Flip-Flop Setup time tsu = 3.0 (min) Flip-flop Hold time th = 0.0 (min) Logic gate delay tpLH (min) = 1.5, tpLH (max) = 3.0 tpHL (min) = 1.0, tpHL (max) = 2.5 What is the maximum clock speed for the circuit when: a) b) There are 4 levels of combinatorial logic delay between flip-flops? There are 8 levels of combinatorial logic delay between flip-flops? D QH Flip-flop Combinational logic block HOH D Q Flip-flop Figure 1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts