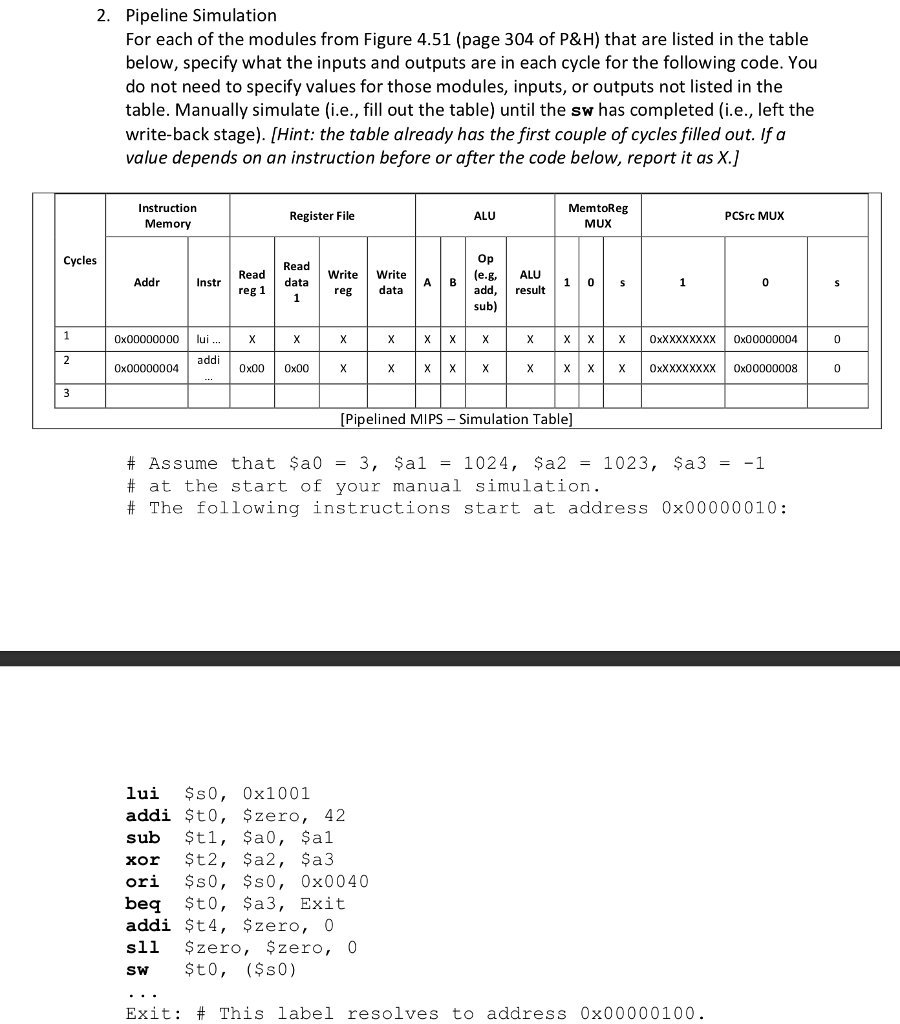

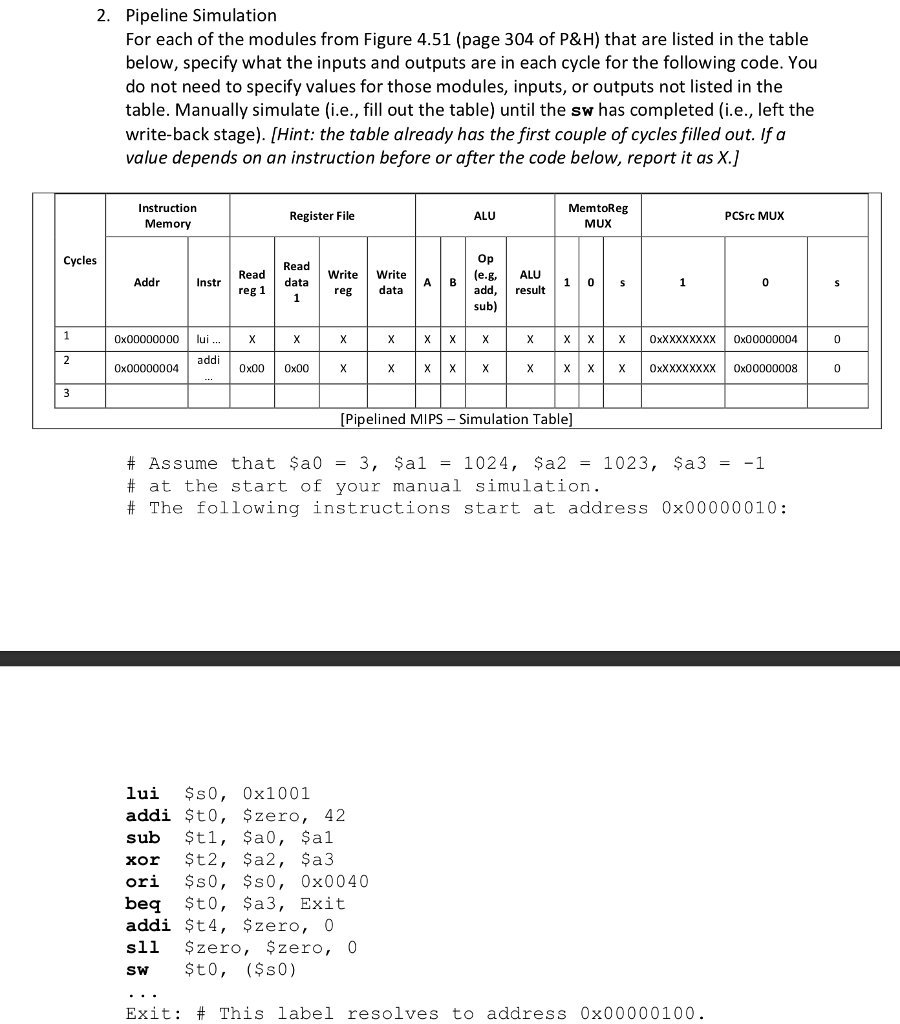

Pipeline Simulation For each of the modules from Figure 4.51 (page 304 of P&H) that are listed in the table below, specify what the inputs and outputs are in each cycle for the following code. You do not need to specify values for those modules, inputs, or outputs not listed in the table. Manually simulate (i.e., fill out the table) until the sw has completed (i.e., left the write-back stage). [Hint: the table already has the first couple of cycles filled out. If a value depends on an instruction before or after the code below, report it as X.]

2. Pipeline Simulation For each of the modules from Figure 4.51 (page 304 of P&H) that are listed in the table below, specify what the inputs and outputs are in each cycle for the following code. You do not need to specify values for those modules, inputs, or outputs not listed in the table. Manually simulate (i.e., fill out the table) until the sw has completed (i.e., left the write-back stage). [Hint: the table already has the first couple of cycles filled out. If a value depends on an instruction before or after the code below, report it as X.] Instruction Memory MemtoReg MUX Register File ALU PCSrc MUX Cycles op Instr Read Read data WriteWrite reg data Addr A B(e.8ALU add, result sub) 0x00000000X X XX0xXXXXXXXX 0x00000004 0 addiox00 0x00000004 X XXOxXXXXXXXX 0x00000008 Pipelined MIPS Simulation Table # Assume that $a0 = 3, $a1 = 1024, $a2 = 1023, $a3 = # at the start of your manual simulation # The following instructions start at address 0x00000010: 1 lui s0, 0x1001 addi $t0, $zero, 4.2 xor $t2, $a2, $a3 ori $s0, $s0, 0x0040 beq $t0, $a3, Exit addi $t4, zero, 0 sll $zero, $zero, 0 sw $t0, (s0) Exit: # This label resolves to address 0x00000100 2. Pipeline Simulation For each of the modules from Figure 4.51 (page 304 of P&H) that are listed in the table below, specify what the inputs and outputs are in each cycle for the following code. You do not need to specify values for those modules, inputs, or outputs not listed in the table. Manually simulate (i.e., fill out the table) until the sw has completed (i.e., left the write-back stage). [Hint: the table already has the first couple of cycles filled out. If a value depends on an instruction before or after the code below, report it as X.] Instruction Memory MemtoReg MUX Register File ALU PCSrc MUX Cycles op Instr Read Read data WriteWrite reg data Addr A B(e.8ALU add, result sub) 0x00000000X X XX0xXXXXXXXX 0x00000004 0 addiox00 0x00000004 X XXOxXXXXXXXX 0x00000008 Pipelined MIPS Simulation Table # Assume that $a0 = 3, $a1 = 1024, $a2 = 1023, $a3 = # at the start of your manual simulation # The following instructions start at address 0x00000010: 1 lui s0, 0x1001 addi $t0, $zero, 4.2 xor $t2, $a2, $a3 ori $s0, $s0, 0x0040 beq $t0, $a3, Exit addi $t4, zero, 0 sll $zero, $zero, 0 sw $t0, (s0) Exit: # This label resolves to address 0x00000100