Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Please answer clearly by your own A computer is being designed using a microprocessor with a 20-bit address bus (AO - A19). The 1MB address

Please answer clearly by your own

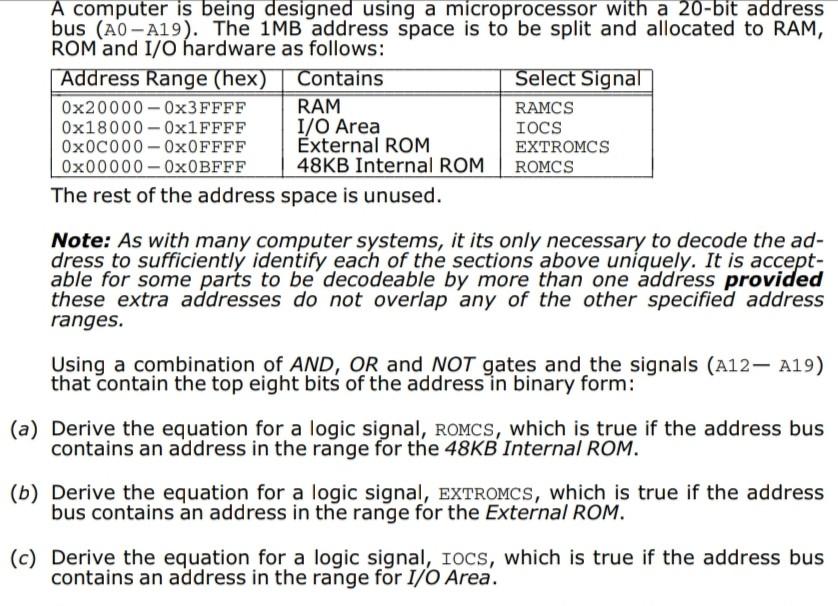

A computer is being designed using a microprocessor with a 20-bit address bus (AO - A19). The 1MB address space is to be split and allocated to RAM, ROM and I/O hardware as follows: Address Range (hex) Contains Select Signal Ox20000-0x3FFFF RAM RAMCS Ox18000-0x1FFFF I/O Area IOCS OxOC000-Ox0FFFF External ROM EXTROMCS 0x00000 - Ox0BFFF 48KB Internal ROM ROMCS The rest of the address space is unused. Note: As with many computer systems, it its only necessary to decode the ad- dress to sufficiently identify each of the sections above uniquely. It is accept- able for some parts to be decodeable by more than one address provided these extra addresses do not overlap any of the other specified address ranges. Using a combination of AND, OR and NOT gates and the signals (A12- A19) that contain the top eight bits of the address in binary form: (a) Derive the equation for a logic signal, ROMCS, which is true if the address bus contains an address in the range for the 48KB Internal ROM. (b) Derive the equation for a logic signal, EXTROMCS, which is true if the address bus contains an address in the range for the External ROM. (c) Derive the equation for a logic signal, IOCS, which is true if the address bus contains an address in the range for I/O Area. A computer is being designed using a microprocessor with a 20-bit address bus (AO - A19). The 1MB address space is to be split and allocated to RAM, ROM and I/O hardware as follows: Address Range (hex) Contains Select Signal Ox20000-0x3FFFF RAM RAMCS Ox18000-0x1FFFF I/O Area IOCS OxOC000-Ox0FFFF External ROM EXTROMCS 0x00000 - Ox0BFFF 48KB Internal ROM ROMCS The rest of the address space is unused. Note: As with many computer systems, it its only necessary to decode the ad- dress to sufficiently identify each of the sections above uniquely. It is accept- able for some parts to be decodeable by more than one address provided these extra addresses do not overlap any of the other specified address ranges. Using a combination of AND, OR and NOT gates and the signals (A12- A19) that contain the top eight bits of the address in binary form: (a) Derive the equation for a logic signal, ROMCS, which is true if the address bus contains an address in the range for the 48KB Internal ROM. (b) Derive the equation for a logic signal, EXTROMCS, which is true if the address bus contains an address in the range for the External ROM. (c) Derive the equation for a logic signal, IOCS, which is true if the address bus contains an address in the range for I/O AreaStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started