Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Please help me write a controller module in verilog that follows the behavior of the table and utilizes the module defintion of the skeleton code

Please help me write a controller module in verilog that follows the behavior of the table and utilizes the module defintion of the skeleton code given below. Thank you!

timescale ns ps

Module definition

module Controller

Opcode

ALUSrc MemtoReg RegWrite MemRead MemWrite

ALUOp

;

Define the input and output signals

Define the Controller modules behavior

endmodule Controller

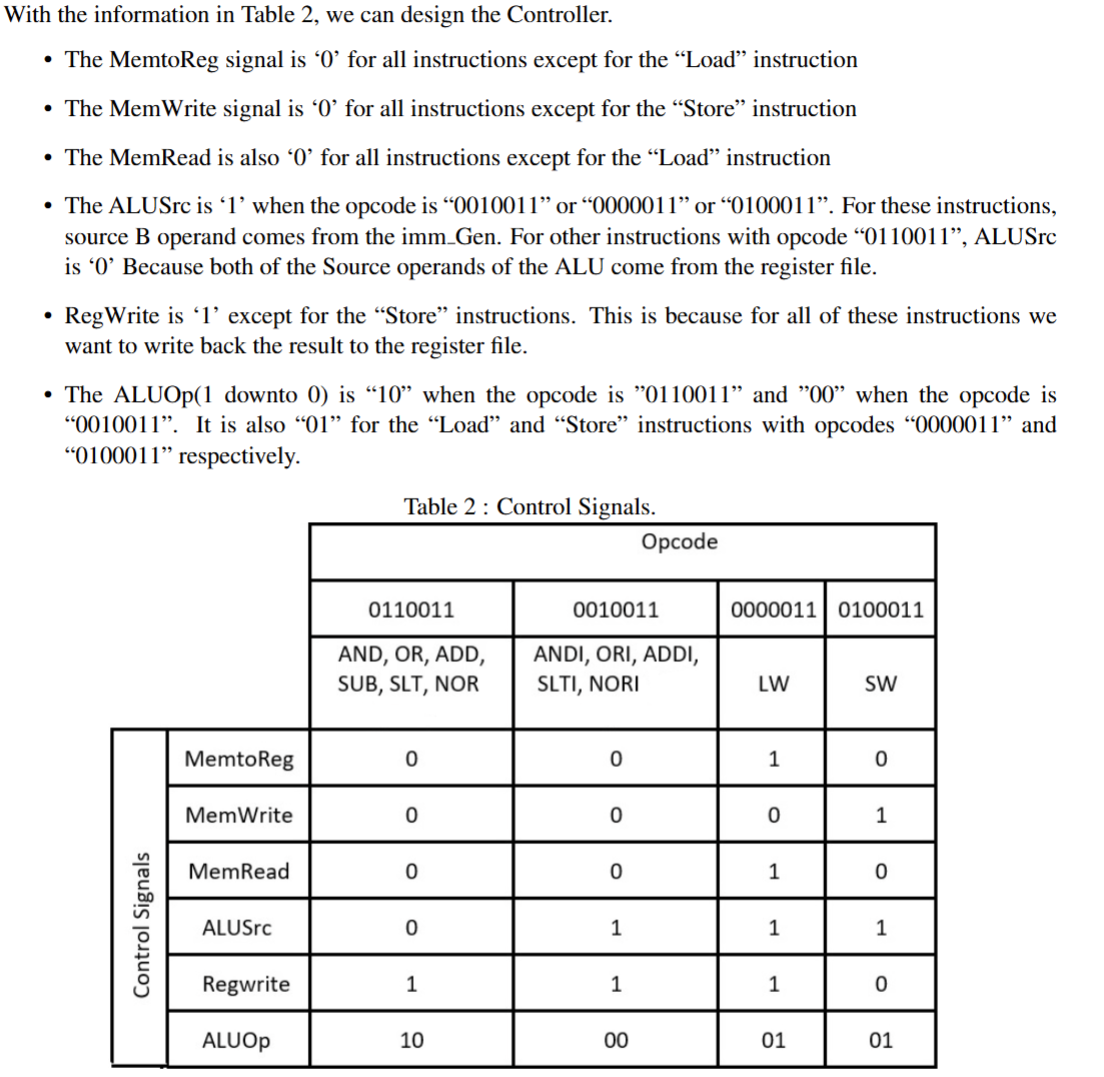

With the information in Table we can design the Controller.

The MemtoReg signal is for all instructions except for the "Load" instruction

The MemWrite signal is for all instructions except for the "Store" instruction

The MemRead is also for all instructions except for the "Load" instruction

The ALUSrc is when the opcode is or or For these instructions, source B operand comes from the immGen. For other instructions with opcode ALUSrc is Because both of the Source operands of the ALU come from the register file.

RegWrite is except for the "Store" instructions. This is because for all of these instructions we want to write back the result to the register file.

The ALUOp downto is when the opcode is and when the opcode is It is also for the "Load" and "Store" instructions with opcodes and respectively.

Table : Control Signals.

tableOpcode,tableAND OR ADD,SUB SLT NORtableANDI ORI, ADDI,SLTI NORILWSWtableMemtoReg,MemWriteMemReadALUSrcRegwriteALUOp

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started