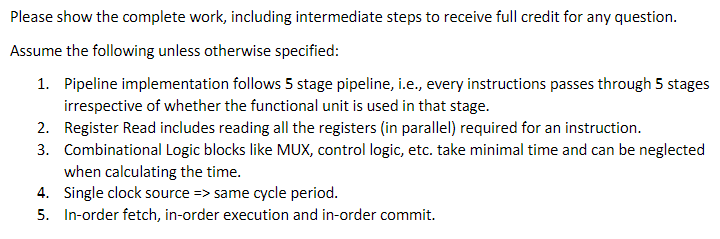

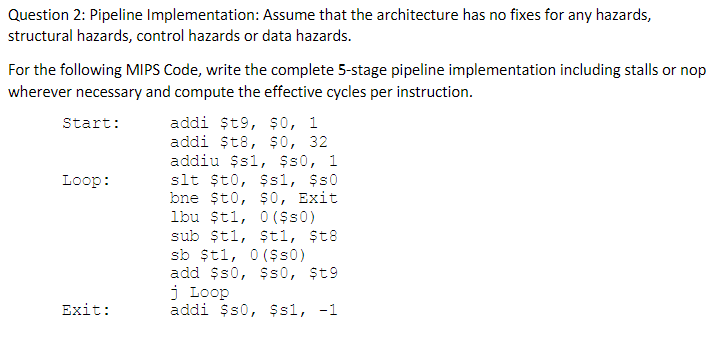

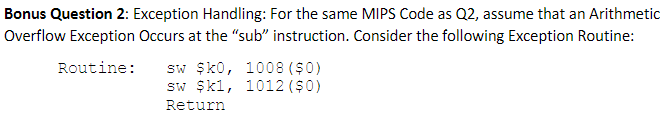

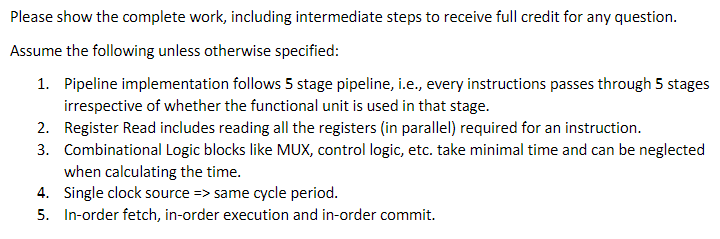

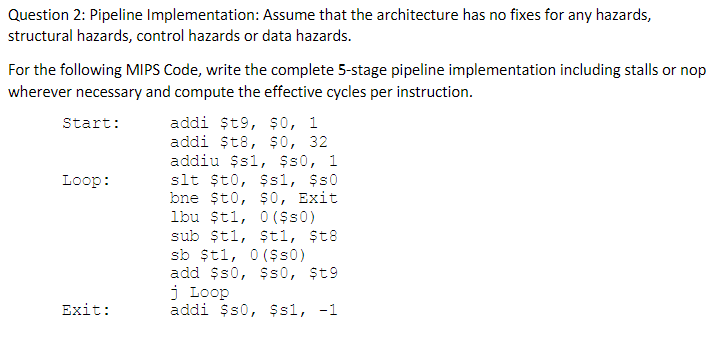

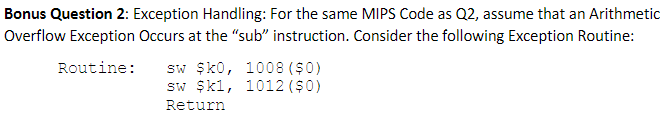

Please show the complete work, including intermediate steps to receive full credit for any question. Assume the following unless otherwise specified: 1. Pipeline implementation follows 5 stage pipeline, i.e., every instructions passes through 5 stages irrespective of whether the functional unit is used in that stage. 2. Register Read includes reading all the registers (in parallel) required for an instruction. 3. Combinational Logic blocks like MUX, control logic, etc. take minimal time and can be neglected when calculating the time. 4. Single clock source > same cycle period. 5. In-order fetch, in-order execution and in-order commit. Question 2: Pipeline Implementation: Assume that the architecture has no fixes for any hazards, structural hazards, control hazards or data hazards. For the following MIPS Code, write the complete 5-stage pipeline implementation including stalls or nop wherever necessary and compute the effective cycles per instruction. Start:Loop:Exit:addi$t9,$0,1addi$t8,$0,32addiu$s1,$s0,1slt$t0,$s1,$s0bne$t0,$0,Exitlou$t1,0($s0)sub$t1,$t1,$t8sb$t1,0($s0)add$s0,$s0,$t9jLoopaddi$s0,$s1,1 Bonus Question 2: Exception Handling: For the same MIPS Code as Q2, assume that an Arithmetic Overflow Exception Occurs at the "sub" instruction. Consider the following Exception Routine: Routine: sw$k0,1008($0) Sw $k1,1012($0) Return Please show the complete work, including intermediate steps to receive full credit for any question. Assume the following unless otherwise specified: 1. Pipeline implementation follows 5 stage pipeline, i.e., every instructions passes through 5 stages irrespective of whether the functional unit is used in that stage. 2. Register Read includes reading all the registers (in parallel) required for an instruction. 3. Combinational Logic blocks like MUX, control logic, etc. take minimal time and can be neglected when calculating the time. 4. Single clock source > same cycle period. 5. In-order fetch, in-order execution and in-order commit. Question 2: Pipeline Implementation: Assume that the architecture has no fixes for any hazards, structural hazards, control hazards or data hazards. For the following MIPS Code, write the complete 5-stage pipeline implementation including stalls or nop wherever necessary and compute the effective cycles per instruction. Start:Loop:Exit:addi$t9,$0,1addi$t8,$0,32addiu$s1,$s0,1slt$t0,$s1,$s0bne$t0,$0,Exitlou$t1,0($s0)sub$t1,$t1,$t8sb$t1,0($s0)add$s0,$s0,$t9jLoopaddi$s0,$s1,1 Bonus Question 2: Exception Handling: For the same MIPS Code as Q2, assume that an Arithmetic Overflow Exception Occurs at the "sub" instruction. Consider the following Exception Routine: Routine: sw$k0,1008($0) Sw $k1,1012($0) Return