please solve

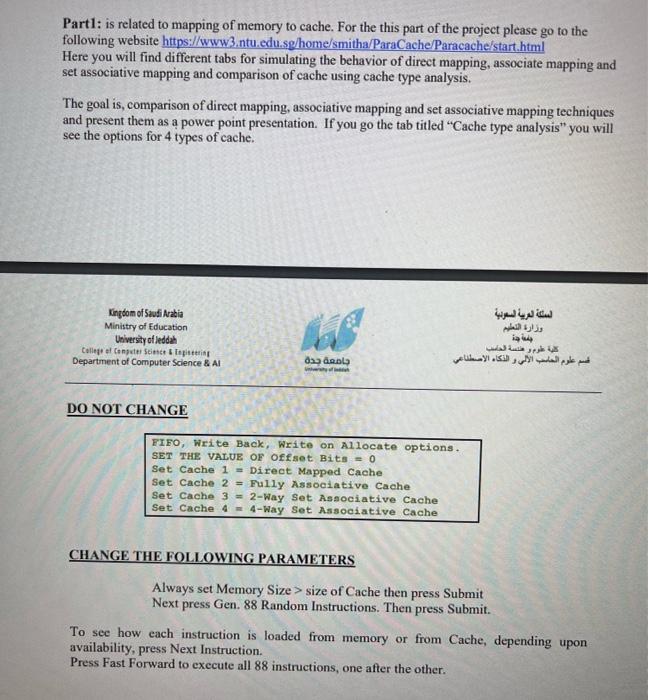

Part1: is related to mapping of memory to cache. For the this part of the project please go to the following website https://www3,ntu.edu.sg/home/smitha/ParaCache/Paracache/start.html Here you will find different tabs for simulating the behavior of direct mapping, associate mapping and set associative mapping and comparison of cache using cache type analysis. The goal is, comparison of direct mapping, associative mapping and set associative mapping techniques and present them as a power point presentation. If you go the tab titled "Cache type analysis" you will see the options for 4 types of cache. CHANGE THE FOLLOWING PARAMETERS Always set Memory Size > size of Cache then press Submit Next press Gen. 88 Random Instructions. Then press Submit. To see how each instruction is loaded from memory or from Cache, depending upon availability, press Next Instruction. Press Fast Forward to execute all 88 instructions, one after the other. 1. For All caches (Direct Mapping) a. Set the size of Cache so that Direct Mapping has the maximum hit ratio and minimum miss ratio? b. How can you increase the hit ratio in case of direct mapping by changing some of size of Caches? c. In presentation, show the pictures from the simulator containing the values used and results obtained. Also, give reasons why the hit ratio increases when you change the size of caches? d. Explain the reason for the number of bits being used for Tag and for the number of bits required for RAM address? 2. For All caches (Fully Associative Mapping) a. Set the size of Cache so that Fully Associative Mapping has the maximum hit ratio and minimum miss ratio? b. How can you increase the hit ratio in case of Fully Associative Mapping by changing some of size of Caches? c. In presentation, show the pictures from the simulator containing the values used and results obtained. Also, give reasons why the hit ratio increases when you change the size of caches? d. Explain the reason for the number of bits being used for Tag and for the number of bits required for RAM address? 3. For All caches (4-way Associative Mapping) a. Set the size of Cache so that 4-way Associative Mapping has the maximum hit ratio and minimum miss ratio? b. How can you increase the hit ratio in case of 4-way Associative Mapping by changing some of size of Caches? c. In presentation, show the pictures from the simulator containing the values used and results obtained. Also, give reasons why the hit ratio increases when you change the size of caches? d. Explain the reason for the number of bits being used for Tag and for the number of bits required for RAM address? Part2: Write an Assembly Language Program that: 1. Ask the user to enter three digits octal number (base 8). Hint: The program should only accept the digits {0,1,2,3,4,5,6,7} 2. Convert the input into decimal number. 3. Print a message to the user with the result 4. The code with run results should be shown in your presentation