Question

Problem 1 (40 Points) Design a MIPS processor supporting only the R-type and the liw rd, rs, rt instructions. The liw rd, rs, rt instruction

Problem 1

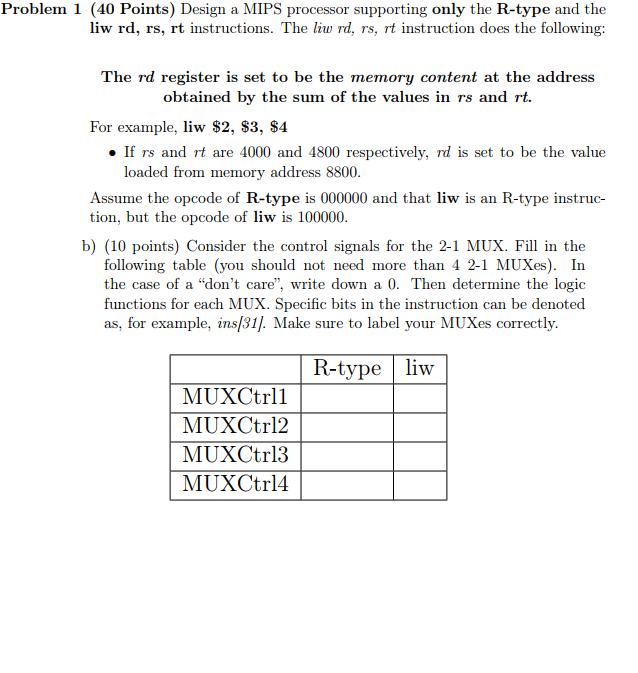

(40 Points) Design a MIPS processor supporting only the R-type and the liw rd, rs, rt instructions. The liw rd, rs, rt instruction does the following: The rd register is set to be the memory content at the address obtained by the sum of the values in rs and rt. For example, liw $2, $3, $4 If rs and rt are 4000 and 4800 respectively, rd is set to be the value loaded from memory address 8800. Assume the opcode of R-type is 000000 and that liw is an R-type instruction, but the opcode of liw is 100000.

b) (10 points) Consider the control signals for the 2-1 MUX. Fill in the following table (you should not need more than 4 2-1 MUXes). In the case of a dont care, write down a 0. Then determine the logic functions for each MUX. Specific bits in the instruction can be denoted as, for example, ins[31]. Make sure to label your MUXes correctly.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started