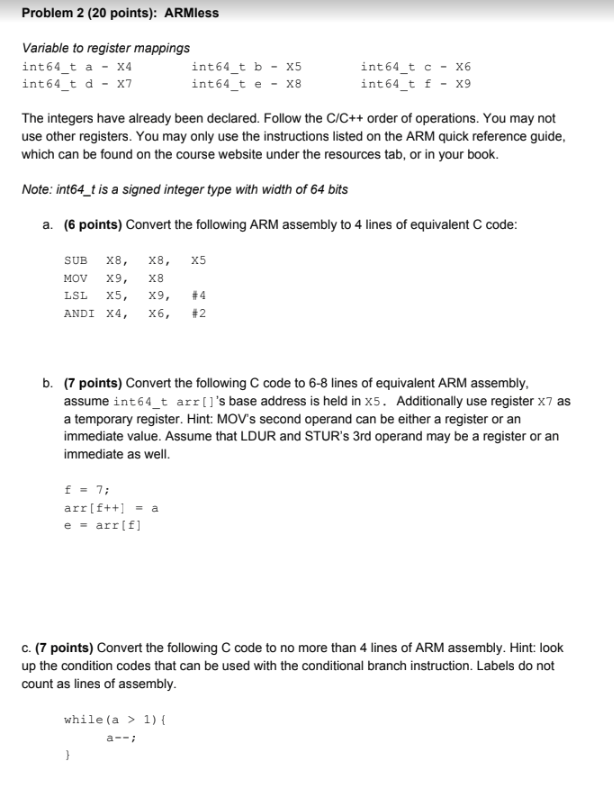

Problem 2 (20 points): ARMless Variable to register mappings int64 t a -x4 int64 td-X7 int64 tb-X5 int64 te-X8 int64 tc-x6 use other registers. You may only use the instructions listed on the ARM quick reference guide which can be found on the course website under the resources tab, or in your book Note: int64 t is a signed integer type with width of 64 bits (6 points) Convert the following ARM assembly to 4 lines of equivalent C code SUB X8, x8, X5 LSL X5, X9, #4 a. ANDI X4, X6, #2 b. (7 points) Convert the following C code to 6-8 lines of equivalent ARM assembly assume int64_t arr[1's base address is held in x5. Additionally use register x7 as a temporary register. Hint: MOVs second operand can be either a register or an immediate value. Assume that LDUR and STUR's 3rd operand may be a register or an immediate as well. arrf++a earrf] c. (7 points) Convert the following C code to no more than 4 lines of ARM assembly. Hint: look up the condition codes that can be used with the conditional branch instruction. Labels do not count as lines of assembly while (a > 1) Problem 2 (20 points): ARMless Variable to register mappings int64 t a -x4 int64 td-X7 int64 tb-X5 int64 te-X8 int64 tc-x6 use other registers. You may only use the instructions listed on the ARM quick reference guide which can be found on the course website under the resources tab, or in your book Note: int64 t is a signed integer type with width of 64 bits (6 points) Convert the following ARM assembly to 4 lines of equivalent C code SUB X8, x8, X5 LSL X5, X9, #4 a. ANDI X4, X6, #2 b. (7 points) Convert the following C code to 6-8 lines of equivalent ARM assembly assume int64_t arr[1's base address is held in x5. Additionally use register x7 as a temporary register. Hint: MOVs second operand can be either a register or an immediate value. Assume that LDUR and STUR's 3rd operand may be a register or an immediate as well. arrf++a earrf] c. (7 points) Convert the following C code to no more than 4 lines of ARM assembly. Hint: look up the condition codes that can be used with the conditional branch instruction. Labels do not count as lines of assembly while (a > 1)