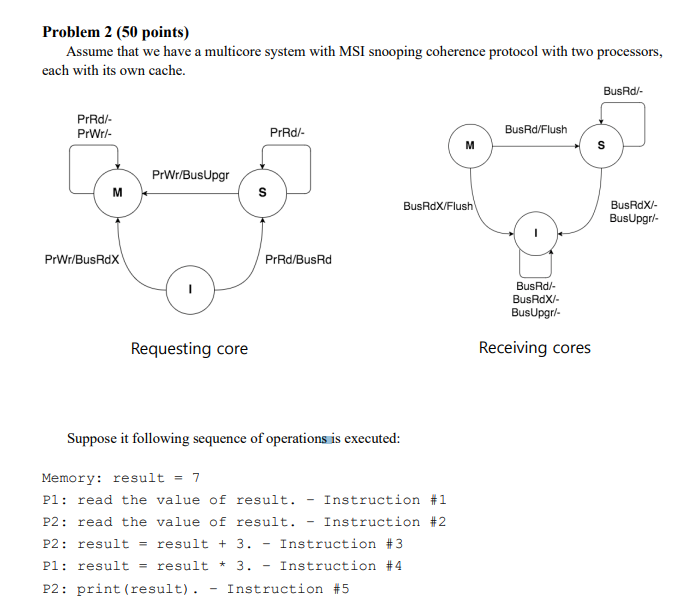

Question: Problem 2 (50 points) Assume that we have a multicore system with MSI snooping coherence protocol with two processors, each with its own cache.

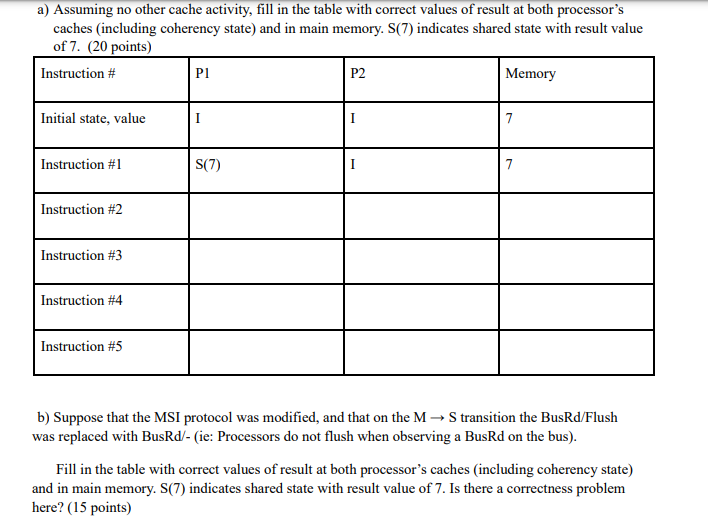

Problem 2 (50 points) Assume that we have a multicore system with MSI snooping coherence protocol with two processors, each with its own cache. PrRd/- PrWr/- M PrWr/BusRdX PrWr/BusUpgr Requesting core S PrRd/- PrRd/BusRd M BusRdX/Flush) Suppose it following sequence of operations is executed: Memory: result = 7 Pl: read the value of result. - Instruction #1 P2: read the value of result. Instruction #2 P2: result = result + 3. Instruction #3 P1: result = result * 3. Instruction #4 P2: print (result). Instruction #5 BusRd/Flush BusRd/- BusRdX/- BusUpgr/- Receiving cores BusRd/- S BusRdX/- BusUpgr/- a) Assuming no other cache activity, fill in the table with correct values of result at both processor's caches (including coherency state) and in main memory. S(7) indicates shared state with result value of 7. (20 points) Instruction # Initial state, value Instruction #1 Instruction #2 Instruction #3 Instruction #4 Instruction #5 P1 I S(7) P2 Memory 7 7 b) Suppose that the MSI protocol was modified, and that on the M S transition the BusRd/Flush was replaced with BusRd/- (ie: Processors do not flush when observing a BusRd on the bus). Fill in the table with correct values of result at both processor's caches (including coherency state) and in main memory. S(7) indicates shared state with result value of 7. Is there a correctness problem here? (15 points) c) Suppose that on the I S transition, the PrRd/BusRd was replaced with PrRd/BusRdX (ie: When the processor reads a value, it generates a BusRdX transaction instead of a BusRd transaction.) Fill in the table with correct values of result at both processor's caches (including coherency state) and in main memory. S(7) indicates shared state with result value of 7. Is there a correctness problem here, or any other performance problem? What happens if P1 tries to access the result value after instruction# 5? (15 points)

Step by Step Solution

There are 3 Steps involved in it

Solutions Step 1 Explanation Solution of the question Lets tackle this step by step a Instruction P1 P2 Memory Initial state value I I 7 Instruction1 S7 I 7 Instruction2 S7 S7 7 Instruction3 M10 S10 1... View full answer

Get step-by-step solutions from verified subject matter experts